# THE COMPUTER JOURNAL®

For Those Who Interface, Build, and Apply Micros

Vol. II, No. 4

\$2.50 US

# Build a VIC-20 EPROM Programmer Page 1

# Multi-user: CP/NET page 8

# Build a High-Resolution S-100 Graphics Board Part Three:Construction Page 10

System Integration

Part Three: CP/M 3.0 page 17

Linear Optimization with Micros Page 23

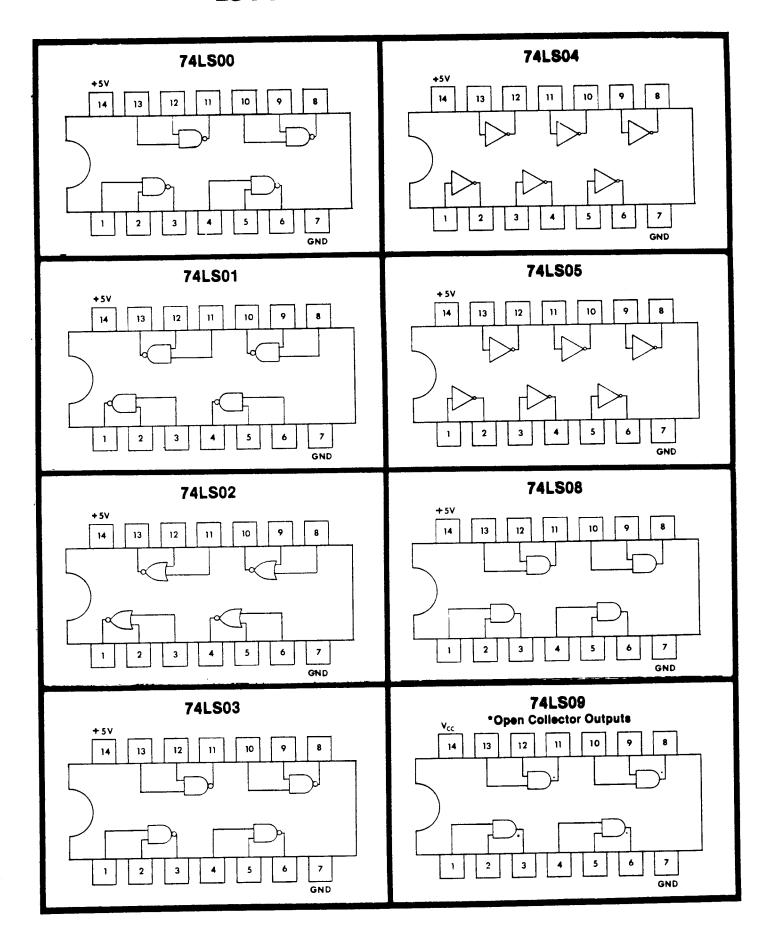

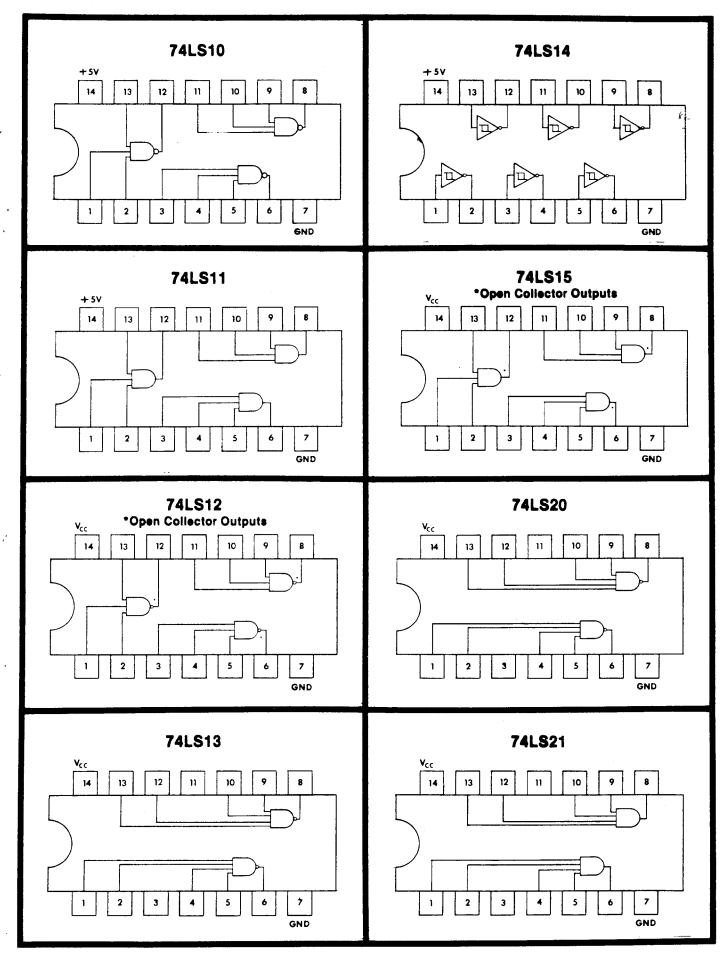

LSTTL Reference Chart Page 25

# Editor's Page

# The Customer is Tired of Being Ignored!

Many of the companies in the microcomputer industry have developed a very simple customer relations policy—they just ignore correspondence and phone calls. This may have been a cost-effective way of handling the problem in an expanding market filled with eager and unsophisticated buyers, but experienced business people will not put up with this shoddy treatment in the current buyer's market.

The microcomputer industry is still structured around the pioneer companies started by a technically oriented entrepreneur with little cash and no business experience who ran the business out of a spare bedroom. These undercapitalized, understaffed enterprises made millions because there was no competition, and because the owners were too busy taking money to the bank to worry about the customer. Their problem was how to expand fast enough to meet the unfilled demands. It didn't matter if the customer was unsatisfied because the product was already paid for (they don't give refunds if the product doesn't work), and there were dozens of new buyers to replace every lost customer.

Good documentation and customer support are extremely important for business equipment and software. With the large number of vendors competing for your dollar today, your decision to buy any micro product should be largely based on how you will be treated by the company after the purchase. In order to help you compare customer support policies, The Computer Journal is surveying vendors and will publish the customer relations policy with the addresses and phone numbers. We will also encourage them to submit bug fixes, customization notes, and interfacing information for publication.

Realizing that what happens in the real world is often different than the published policy, we will also publish the experiences of our readers, after giving the vendors the opportunity to

respond. We do need your experiences with vendors (both the good and the bad) to help others avoid the companies with poor products and miserable customer relations.

Our loyalty is to our readers, and not to any possible advertisers. We will not hesitate to report bad products and poor customer support, but we will need copies of correspondence and records of phone calls which we can present to the vendors prior to publication.

We have had a bad experience with a computer system we purchased recently. We wrote twice for information on an upgrade, but they have not answered our letters. We liked their product, but will not purchase any other equipment from them or recommend their equipment to anyone else. We are sending copies of the letters to the vendor for their reply before publishing the details.

This magazine is published for you, and it will only be as good as you make it. Take time to tell us about your vendor experiences, and share your bug fixes, customization patches, interfacing information and technical tips with the other readers.

The Computer Journal® is published 12 times a year. Annual subscription is \$24 in the U.S., \$30 in Canada, and \$48 airmail in other countries.

Entire contents copyright © 1984 by The Computer Journal

Postmaster: Send address changes to: The Computer Journal, P.O. Box 1697, Kalispell, MT 59903-1697.

Address all editorial, advertising and subscription inquires to: The Computer Journal, P.O. Box 1697, Kalispell, MT 59903-1697.

# by Neil Bungard

#### Introduction

About a month ago I was presented with an interesting problem. I had acquired a Z-80 based S-100 bus microcomputer which had no operating software installed on it. I had an operating system stored on paper tape, but I needed the operating system on an EPROM before my system would run it. The EPROM programmers that I looked at were too expensive to justify buying simply to program one EPROM, so I looked for an alternative solution. It so happened that I had recently purchased a VIC-20, so I decided to design an EPROM programmer attachment for the VIC-20 and use the VIC-20 to transfer the Z-80 operating software from the paper tape to the EPROM. The VIC-20 solved my EPROM programming problem with exceptional grace. With the VIC-20 and ten dollars worth of additional hardware, I was able to enter, inspect, program, and verify data on both 2716 (2K by 8) and 2732 (4K by 8) EPROMs. In addition, the VIC-20 EPROM programmer has features not found on even the most expensive EPROM programmers. Data to be programmed into the EPROM can be entered from cassette tape, 5" diskettes, any RS-232 device, from the VIC-20 keyboard, or even from another EPROM.

# Circuit Description

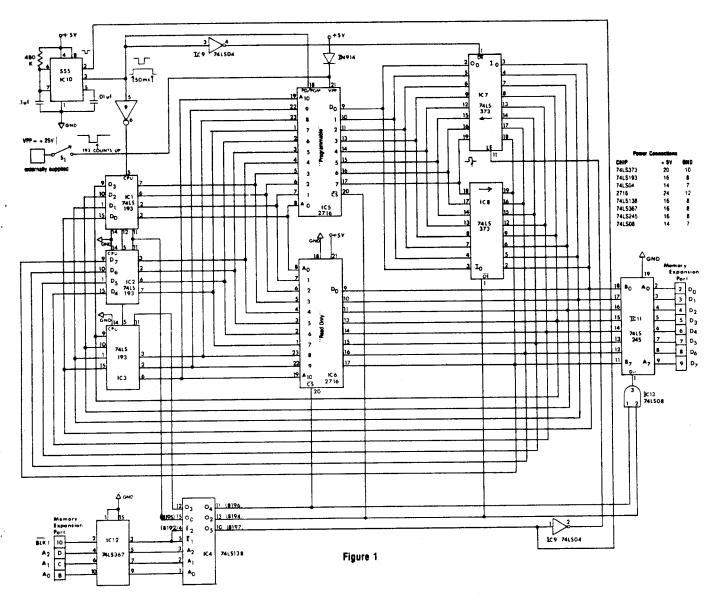

The VIC-20 EPROM programmer circuit diagram is shown in Figure 1. This circuit was designed to program 2716 (2K by 8) EPROMs, but with minor circuit modifications the VIC-20 can program 2732 (4K by 8) EPROMs as well. These modifications will be explained in detail, and can be hard wired or wired so that "personality modules" can be inserted to select between programming 2716s or 2732s.

The VIC-20 EPROM Programmer performs four basic functions:

- 1. It can set the address of where data trasfers are to begin on the EPROM.

- 2. It can read data from a "read only" EPROM. This is used in the EPROM duplicate mode.

- 3. It can read data from a "programable" EPROM. This is used in the program verification mode.

- 4. It can program an EPROM. This, of course, is used in the program mode.

To obtain an understanding of the operation of the EPROM programmer circuit in each mode, let us look at these four basic functions separately.

The first function, address selection, is accomplished by loading three presettable counters with the beginning address of where you wish to store or retrieve data on the EPROM. The counters are 74LS193s (IC 1, 2, and 3 in Figure 1). The inputs of the counters are tied through buffers to the

data bus of the VIC-20. The outputs of the counters are connected to the address lines of the 2716s so that the values loaded into the 74LS193s will be present on the address lines of the EPROMs. With an address value loaded into the 74LS193s and present on both EPROMs, a memory read from either EPROM or a memory write to the programable EPROM can be accomplished. Once the data transfer operation is accomplished, the selected address can either be advanced in increments of one, or a new address can be loaded into the counters.

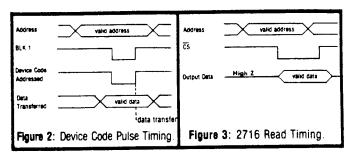

Values are loaded into selected counters by the VIC-20 via an Input/Output (I/O) device code generator (IC4). The device code generator (a 74LS138) is a three line to eight line decoder. Its three input lines are tied through buffers to the three lowest order address bits of the VIC-20 address bus. When the VIC-20 wants to accomplish an information transfer (either Input or Output) it places the address of where the data exchange is to take place onto pins 1, 2, and 3 of the 74LS138. The VIC-20 then pulses "BLK1" to a logic 0. This generates a device code pulse on one of eight output pins on the 74LS138 which accomplishes a data transfer to/from one of eight unique address locations defined by the values of A0, A1, and A2. Table 1 shows the eight data transfer pulses generated on the EPROM programmer. Figure 2 is the timing diagram of the device code pulse generated.

With reference to Table 1, the following software is required to operate the device select hardware and set a given address location for a memory transfer:

10 POKE 8195,0 20 POKE 8192,0

This program addresses memory location 0 (decimal) on the EPROMs. 10 POKE 8195,0 loads the four higher order bits of the 12 bit address into address counter IC3 by placing the high order address value on data bus bits D0 through D3 and pulsing pin 11 of IC3 to a logic 0. 20 POKE 8192,0 loads the eight low order address bits into counters IC1 and IC2

| Device<br>Code<br>Address | Output<br>Pin of<br>74LS138 | Use of Device Code Pulse                               |

|---------------------------|-----------------------------|--------------------------------------------------------|

| 8192                      | 15                          | loads the 8 lower order bits of the address counter    |

| 8193                      | NA                          | NA                                                     |

| 8194                      | 13                          | transfers data from "programmable" EPROM to the VIC 20 |

| 8195                      | 12                          | Loads the 4 higher order bits of the address counters  |

| 8196                      | 11                          | transfers data from "read only" EPROM to the VIC 20    |

| 8197                      | 10                          | programs EPROM and increments the address counters     |

| 8198                      | NA                          | NA                                                     |

| 8199                      | NΑ                          | NA                                                     |

|                           |                             | Table 1                                                |

by placing the EPROM address value on the data bus and pulsing pin 11 of IC1 and IC2 to a logic 0. To advance the counters, which increments the selected address, the following instructions are required:

10 POKE 8197,0

20 FOR I = 0 TO 50: NEXT I

POKE 8197,0 generates a device code pulse on pin 10 of the 74LS138 (IC4). This low going pulse triggers a monostable multivibrator (IC10), which is configured to generate a 50ms high-going pulse. This 50ms pulse is required in the EPROM programming sequence which will be discussed later. The output of the monostable (pin 3, IC10) is connected, through an inverter, to the "up-count" input of IC1. If the READ/PROGRAM switch (S1, Figure 1) is in the READ position (open), the selected address will be advanced by one when the monostable times out, but no EPROM memory However, programmed. location will be READ/PROGRAM switch is in the PROGRAM (closed) position when the POKE 8197,0 instruction is executed, address location 0 (decimal) on the programmable EPROM will be loaded with a 0 before the address counter (IC1) is

advanced. Details of this sequence will be discussed further in the explanation of the programming mode.

The important thing to remember in our discussion thus far is that for the purpose of reading either EPROM, the READ/PROGRAM switch must be in the READ position. The second instruction 20 FOR I = 0 TO 50: NEXT I is a software time delay to allow the monostable to time out before any other instructions are executed. Even though the 50ms pulse is only used in the programming mode it is still generated in the read and verify modes to advance the counters. It is the trailing edge of this pulse that always advances the address counters and thus must be accounted for in all the modes of operation.

The second basic function performed by the EPROM programmer is reading data from the "read only" EPROM. In order to do this, the memory address of where the read operation is to occur is loaded into the memory address counters as previously explained. Next, a memory read operation is performed by the VIC-20 which generates an input device code pulse on pin 11 of the device code pulse generator IC4. Pin 11 of IC4 is connected to the chip select

(CS) input of the read only 2716 (IC6). When the CS input (pin 20) is pulsed low (with pin 18 tied low and pin 21 held high) data flows from the memory location addressed on the EPROM into the VIC-20. Figure 3 shows the timing diagram of the 2716 read operation. The following software is required to perform the read only EPROM read operation:

10 POKE 8195,0 20 POKE 8192,0 30 A = PEEK(8196)

The BASIC instructions in lines 10 and 20 set the memory address of where the read operation will occur. These two instructions have been previously explained. The instruction 30 A = PEEK(8196) generates a device code pulse on pin 11 of IC4 which inputs the data from the addressed memory location, and assigns the data to the variable name "A".

The third basic function performed by the EPROM programmer, reading data from the programmable EPROM, is accomplished in exactly the same manner as reading from the read only EPROM. The only difference is that a device code pulse is generated on pin 13 of IC4 instead of pin 11 as in the case of the read only EPROM. Pin 13 of IC4 is connected to the CS input of the programmable EPROM (pin 20, IC5) and to the output enable (OE) of an octal tristate buffer (pin 1, IC8). Data flows out of this EPROM and through the buffer when pin 13 of the 74LS138 is pulsed low. For the read operation to be accomplished, pin 18 of the 2716 must be at a logic 0 and pin 21 at +5 volts. The software required to read data from the programmable EPROM is:

10 POKE 8195,0 20 POKE 8192,0 30 A = PEEK(8194)

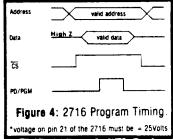

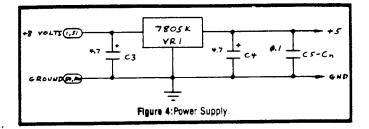

The fourth and last function performed by the EPROM programmer is programming an EPROM. To enter the program mode, the READ/PROGRAM switch must be placed in the PROGRAM position. This applies + 25 volts to pin 21 of the EPROM (IC5), and configures the EPROM to be programmed. Be sure that the 25 volt supply is stable and at no time fluctuates higher than 26 volts. A voltage greater than 26 volts on pin 21 of the EPROM will immediately destroy the EPROM. Next, as was the case when reading the EPROMs, the memory address of where the data transfer is to take place must be loaded into the address counters. By applying an address to the EPROM, placing pin 21 at +25 volts, and insuring that the CS input is at a logic 1, the EPROM is ready to be programmed. Applying a data byte on D0 through D7 of the EPROM, and pulsing pin 18 (PD/PGM) to a logic 1 for 50ms completes the programming operation. The timing diagram for the 2716 programming sequence is shown in Figure 4. The data is applied to the EPROM by the VIC-20 through a memory write operation to location 8197 (decimal). This memory write operation generates a device code pulse on pin 10 of IC4 which latches the outputted data byte into IC7 and triggers the monostable multivibrator (IC10). The monostable applies a 50ms high-going pulse to pin 18 of the EPROM and programs the applied memory address with the data byte latched in IC7. The falling edge of the 50ms programming pulse automatically advances the counters and prepares the next memory address for programming. The following software is required to program address location 0 with decimal value of 100:

10 POKE 8195,0 20 POKE 8192,0 30 POKE 8197,100

# Application Software for the VIC-20 EPROM Programmer

The software required to read, verify, and program 2716 EPROMs will be presented in the following discussion on application software. To perform an EPROM duplication, the contents of a previously programmed EPROM is transferred into the VIC-20's RAM memory. Here the data can be inspected and/or modified if desired. The data is then transferred to a blank EPROM, and a verification is accomplished to ensure that no error occurred in the data transfer. The following software reads the 2048 memory locations of a 2716 and places the data into the VIC-20's RAM memory between locations 5000 (decimal) and 7048(decimal). Insure that the READ/PROGRAM switch is in the READ position, and that the EPROM to be read is inserted into the read only EPROM socket:

10 PRINT "" /clear screen 20 PRINT "SET SWITCH TO" ensure that 30 PRINT "READ POSITION" /READ/PROGRAM 40 PRINT 50 PRINT "HIT RETURN" /switch is in 60 PRINT "TO START" /correct position 70 INPUT X /load high-order 74LS193 80 POKE 8195,0 /load low-order 74LS193 90 POKE 8192.0 100 FOR 1 = 5000 to 7048 /set 2048 RAM spaces /read EPROM 110 A = PEEK(8196)/store value in RAM 120 POKE I,A 130 POKE 8197,0 /advance counters 140 FOR T = 0 to 50:NEXT T /wait for 50ms pulse /to read next location 150 NEXT | 160 PRINT"READ COMPLETE" /prompt user 170 STOP

\*Do not enter comments in right hand column as part of program.

Once the data is in RAM memory, the user can check the code to ensure that the correct 2716 is being duplicated, and/or make minor modifications to the code. Once satisfied with the data in RAM, the data is transferred to a blank EPROM which has been inserted into the programmable EPROM socket. Before the transfer takes place, the READ/PROGRAM switch must be placed in the

PROGRAM position. The following software loads the data which is in the VIC-20's RAM memory space, between address 5000 (decimal) and 7048 (decimal), into a 2716 EPROM:

| 200 PRINT ***                  | /clear the screen        |

|--------------------------------|--------------------------|

| 210 PRINT"SET SWITCH TO"       |                          |

| 220 PRINT"PROGRAM POSITION"    | /ensure that             |

| 230 PRINT                      | /READ/PROGRAM            |

| 240 PRINT"HIT RETURN"          | /switch is in            |

| 250 PRINT"TO START"            | /correct position        |

| 260 INPUT X                    |                          |

| 270 POKE 8195,0                | /load high-order 74LS193 |

| 280 POKE 8192,0                | /load low-order 74LS193  |

| 290 FOR I = 5000 to 7048       | /set 2048 RAM spaces     |

| 300 A = PEEK(I)                | /read data from RAM      |

| 310 POKE 8197,A                | /write data to EPROM     |

| 320 FOR T = 0 to 50:NEXT T     | /wait for 50ms pulse     |

| 330 NEXT I                     | /go read next location   |

| 340 PRINT"PROGRAMMING COMPLETE | ' /prompt user           |

| 350 STOP                       |                          |

When the programming is complete, you should run the following verification program to ensure an accurate EPROM copy:

| 400 PRINT                   | /clear the screen           |

|-----------------------------|-----------------------------|

| 410 PRINT"SET SWITCH TO"    |                             |

| 420 PRINT"READ POSITION"    | /ensure that                |

| 430 PRINT                   | /READ/PROGRAM               |

| 440 PRINT"HIT RETURN"       | /switch is in               |

| 450 PRINT"TO START"         | /correct position           |

| 455 INPUT X                 |                             |

| 460 POKE 8195,0             | /load high-order 74LS193    |

| 470 POKE 8192,0             | /load low-order 74LS193     |

| 480 FOR I = 5000 to 7048    | /set 2048 RAM spaces        |

| 490 A = PEEK(8194)          | /read programmable EPROM    |

| 500 B = PEEK(I)             | /read data from RAM         |

| 510 IF A<>B THEN 570        | /if no match then stop      |

| 520 POKE 8197,0             | /if match, advance counters |

| 530 FOR T = 0 to 50:NEXT T  | /wait for 50ms pulse        |

| 540 NEXT I                  | /go do next comparison      |

| 550 PRINT"DUPLICATION GOOD" | /prompt user                |

| 560 STOP                    |                             |

| 570 PRINT"DUPLICATION BAD"  |                             |

| 580 PRINT''ERROR IN''       | /prompt user                |

| 590 PRINT"ADDRESS";         |                             |

As mentioned in the introduction, EPROMs programmed by the VIC-20 EPROM programmer can receive their data from a number of sources. The only modifications necessary to input data from other sources would be between lines 80 and 160 of the BASIC code. These lines of code move data from some source (another EPROM in the above case) and place the data in the VIC-20's RAM memory. Using the EPROM programmer for my own application, I was required to take data from the VIC-20's RS-232 interface port. The following software accomplishes a data transfer from the RS-232 serial port and places the data into RAM memory locations 5000 (decimal) through 7048 (decimal):

```

80 OPEN 2,2,3 CHR$(163) + CHR*(160) /open the channel, 110 baud, 2 stop bits

90 FOR I = 5000 to 7048 /set 2048 RAM spaces

100 GET 2,A$ /turn on receiver channel

```

110 IF A\$ = "" THEN 100 /ignore a 120 A = PEEK(667) /find ser 130 B = A + 7423 /define b 140 C = PEEK(B) /get data 150 POKE I,C /put data 155 NEXT I /go get a

/ignore a null

/find serial byte in buffer

/define buffer location

/get data from serial port buffer

/put data in RAM memory

/go get next data byte

Another possibility for entering data is through the VIC-20's keyboard. This is not practical for larger data bases, but

in many cases the data is less than a few hundred bytes. For that amount of data the keyboard is not a bad option. The following software will load data into RAM memory starting at location 5000 (decimal), via the vic-20's keyboard:

Enter an "S" to terminate the entry program.

80 PRINT .... /clear the screen /input up to 2048 times 85 FOR ! = 1 to 2048 90 PRINT"ENTER DATA" /prompt user 95 PRINT"BYTE";1 /to enter **100 INPUT A\$** /data byte 105 IF A\$ = "S" THEN 160 /enter S to stop /convert input string to a number 110 A = VAL(AS)/define RAM storage location 115 J = I + 5000/put data in RAM memory 120 POKE J,A 125 PRINT \*\*\*\* /clear the screen 130 NEXT I /go input next data value 135 PRINT''NO MORE ROOM'' 140 PRINT"ON EPROM" /prompt user 145 STOP

#### A Word About Bus Buffering

My original VIC-20 EPROM programmer design did not have Data and Address bus buffers, but I encountered some problems when inserting and removing the EPROMs. When I inserted or installed the "read only" 2716 EPROM, the VIC-20 operating system would crash. I installed the 74 245 data bus buffer and the 74LS367 address bus buffer and the problem disappeared. In general it is a good idea to buffer all of your interface projects. This ensures that you have good "drive" from your computer, and buffering isolates the CPU and other ICs in your computer from your circuit, which could avoid damage to the computer as a result of wiring errors.

# Programming 2732s On the VIC-20 EPROM Programmer

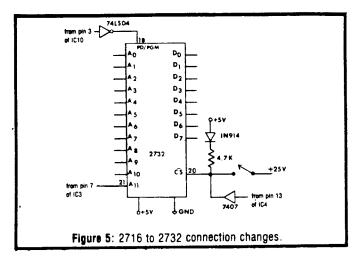

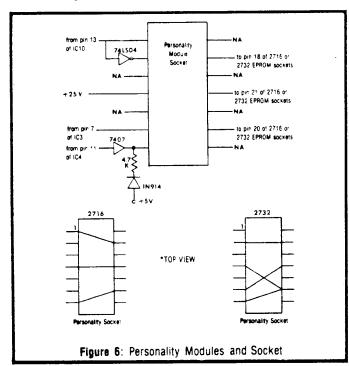

So far only 2716 (2K by 8) EPROMs have been mentioned with reference to the VIC-20 EPROM programmer. The programmer can also program 2732 (4K by 8) EPROMs. There are only three pins which differ between the two EPROMs. These are pins 18, 20, and 21. Figure 5 shows the connection changes necessary to use the VIC-20 EPROM programmer with 2732 EPROMs. These connections can be hard wired to configure the EPROM programmer for 2732s only, or a 14 pin wire wrap socket can be placed on the EPROM programmer board and wired so that jumper wires

can be used to choose between programming 2716s and 2732s. Using this method, personality modules can be constructed which plug into the 14 pin socket. These modules determine whether the programmer is configured for 2716 or 2732 EPROMs by providing the correct jumper wires across the 14 pin socket. Figure 6 shows how the socket is wired to achieve the EPROM selection using the personality modules. Also in Figure 6 are the wiring configurations necessary to construct both the 2716 and the 2732 personality modules. The modules themselves are constructed from 14 pin DIP headers, with jumper wires soldered in place on the header to configure the module.

# Construction of the VIC-20 EPROM Programmer

The VIC-20 EPROM programmer can easily be constructed on a perforated Vectorboard equipped with edgeboard fingers. The edgeboard fingers must be double sided and the pin spacing must be 0.156 inches. The Vectorboard is standard equipment, and can be purchased from most electronic parts distributors.

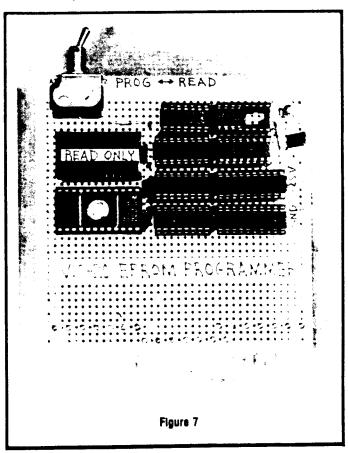

I used wire wrap techniques to construct the EPROM programmer. There are no critical wiring considerations, and the project took less than five hours to construct. A photograph of the VIC-20 EPROM programmer is shown in Figure 7, and a pin assignment of the VIC-20 expansion port is shown in Figure 8 to aid in construction of the programmer.

It should be noted that an external 25 volt power supply is required to program the 2716 and 2732 EPROMs.

The software routines used to program the 2716s will also work with the 2732s. The only changes required in the software routines are in the instructions which account for the 2716's 2048 memory locations. To program 2732s on the VIC-20 without expanding the VIC RAM memory, the 2732's 4K memory should be considered as two 2K blocks. Each 2K block would be programmed separately, which would require two passes through the software routines. On the first pass the address counters should be loaded with a starting address of zero and the first 2K locations would be programmed the same as a 2716. On the second pass the address counters should be loaded with a starting address of 2048 and the next 2K locations would be programmed.

## Conclusion

The software routines presented in this article are what I would consider utility routines. They make the VIC-20 EPROM programmer work, but they are neither instructive nor "friendly" to the user. Providing only the required utility routines allows you to develop an "operating system" to suit your particular needs.

If you want to use the VIC-20 EPROM programmer as a general purpose programming tool for both 2716 and 2732 EPROMs, I would suggest a "prompt and queue" operating system. By "prompt and queue" I mean that the computer prompts the user and asks the user what he/she would like to do. The user in turn enters the proper queue which instructs the computer to perform a specific task. This type of operating system can be implemented nicely with the use of menus. For example, you might have the VIC-20 ask the following question:

WHICH TYPE OF EPROM DO

YOU WISH TO CONSIDER?

If you input "2716", the VIC-20 might print the following

### WHAT FUNCTION DO YOU WISH TO PERFORM?

- 1) EXAMINE CODE ON A 2716 EPROM

- 2) PROGRAM A 2716 EPROM

- 3) DUPLICATE A 2716 EPROM

- 4) ENTER CODE THROUGH KEYBOARD

- 5) ENTER CODE FROM TAPE

- 6) ENTER CODE FROM RS232 PORT

- 7) ENTER CODE FROM DISK

- 8) QUIT

### INPUT YOUR SELECTION?

This menu allows you to perform all the functions which are possible on the VIC-20 EPROM programmer. Selecting a desired function might result in another menu being printed which would help the user choose the proper parameters used in a utility routine. In addition to helping with parameters, the VIC-20 could instruct the user as to which "personality module" to use and when to insert it. Your imagination is your only limitation when designing an operating system for the VIC-20 EPROM programmer. Have

|  |   | 2 |   |  |  |  |  |   |  |   |   |   |   |   |   |   |

|--|---|---|---|--|--|--|--|---|--|---|---|---|---|---|---|---|

|  | _ |   | _ |  |  |  |  | _ |  | _ | _ | _ | _ | _ | _ | • |

| PIN # | TYPE |

|-------|------|

| 1     | GND  |

| 2     | CDO  |

| 3     | CD1  |

| 4     | CD2  |

| 5     | CD3  |

| 6     | CD4  |

| 7     | CD5  |

| 8     | CD6  |

| 9     | CD7  |

| 10    | BLK1 |

| 11    | BLK2 |

| TYPE |

|------|

| BLK3 |

| BLK5 |

| RAM1 |

| RAM2 |

| RAM3 |

| VR/W |

| CR/W |

| IRO  |

| NC   |

| +5V  |

| GND  |

|      |

| PIN # | TYPE |

|-------|------|

| Α     | GND  |

| В     | CA0  |

| С     | CA1  |

| D     | CA2  |

| E     | CA3  |

| F     | CA4  |

| н     | CA5  |

| j     | CA6  |

| K     | CA7  |

| L     | CA8  |

| М     | CA9  |

|       | <del></del>  |

|-------|--------------|

| PIN # | TYPE         |

| N     | CA10         |

| P     | CA11         |

| R     | CA12<br>CA13 |

| T     | 1/02         |

| U     | 1/03         |

| V     | S02          |

| w     | NMI          |

| X     | RESET        |

| Y     | NC           |

| Z     | GND          |

Figure 8

fun with it and drop us a line to let us know what you come

# Did You Miss Any of These Issues?

To order back issues, send \$3.25 (includes postage) to The Computer Journal, PO Box 1697, Kalispell, MT 59903. Allow 3 to 4 weeks for delivery

## Volume 1, Number 1:

- The RS-232-C Serial Interface, Part One

- Telecomputing with the Apple I: Transferring Binary Files

Beginner's Column Part One: Getting Started

- Build an "Epram"

## Volume 1, Number 2:

- File Transfer Programs for CP/M

- The RS-232-C Serial Interface, Part Two

- Build a Hardware Print Spooler, Part One:Background and Design

- A Review of Floppy Disk Formats

- · Sending Morse Code With an Apple]

- Beginner's Column, Part Two: Basic Concepts and Formulas in Electronics

# Volume 1, Number 3:

- Add an 8087 Math Chip to Your Dual Processor Board

- Build an A/D Converter for the Apple [

- ASCII Reference Chart

- . Modems for Micros

- The CP/M Operating System

- Build a Hardware Print Spooler, Part Two:Construction

#### Volume 1, Number 4:

. Optoelectronics, Part One: Detecting, Generating, and Using Light in Electronics

- · Multi-user:An Introduction

- Making the CP/M User Function More Useful

- · Build a Hardware Print Spooler, Part Three: Enhancements

- · Beginner's Column, Part Three: Power Supply Design

# Volume 2, Number 1:

- · Optoelectronics, Part Two: Practical Applications

- Multi-user: Multi-Processor Systems

- True RMS Measurements

- · Gemini-10X: Modifications to Allow both Serial and Parallel Operation

## Volume 2, Number 2:

- · Build a High Resolution S-100 Graphics Board, Part One: Video Displays

- · System Integration, Part One: Selecting System Components

- · Optoelectronics, Part Three: Fiber Optics

- · Controlling DC Motors

- · Multi-User: Local Area Networks

- DC Motor Applications

## Volume 2, Number 3:

- · Heuristic Search in Hi-Q

- · Build a High-Resolution S-100 Graphics Board, Part Two: Theory of Operation

- · Multi-user: Etherseries

- System Integration, Part Two: Disk Controllers and CP/M 2.2 System Generation

# Multi-user

A Column by E.G. Brooner

CP/NET is Digital Research's answer to the networking problem. It is in some ways not a complete network (in fact, it is only the software for one), but it is probably the cheapest way for a clever computer user to "get into" networking. CP/NET can be thought of as an extension of CP/M and MP/M. It takes advantage of the existing features in these very popular operating systems. Using CP/NET is just like using either of its parent systems—all of the same commands are used along with a few new ones to take care of network communication tasks. Basing the network software on what is already there greatly simplifies the entire process.

The latest brochure listed the cost of the CP/NET software at around \$200 for each "workstation," which can be almost any micro equipment running CP/M. Actually, one station has to be MP/M equipped—there is no way around that restriction. And if only one station is so equipped, you really have something similar to a multiprocessor or a very good timesharing system. CP/NET becomes more "network-like" as more MP/M workstations are added.

In talking about other milti-user systems, especially networks, we have made mention of the centrally located disk and printer peripherals that can be accessed by the secondary users. In network terminology these "intelligent" devices are referred to as servers; i.e., disk servers and print servers. A server is usually a dedicated microcomputer handling the communication to and from the peripherals, or between the peripherals and the workstations.

In CP/NET, the server function is performed by part of the additional network software. The MP/M equipped micro, which must be part of any CP/NET, acts as a server for the rest of the network in addition to performing any other functions assigned to it. The MP/M equipped micro can accomodate up to a total of 16 users. If they are terminals, you have a time sharing system; if they are micros with their own processors, the system can be a network.

Let's take a look, first, at MP/M. A time sharing system would consist of one micro running MP/M and some number of terminals sharing its one CPU and its memory, as well as the peripherals. You might find that as you add more than the first two or three terminals, the speed of each user begins to suffer, especially if all of them are quite busy.

If you replace the terminals with individual complete micros, each running CP/M, the situation can be somewhat better. It will not be any better when they are working through or with the main computer, but if they were to disconnect themselves temporarily, they would have the ability to function independently. This is what happens in the simplest possible configuration of CP/NET. The

replacement of terminals with complete computers is basically the dividing point between time sharing and networking.

At this point the CP/NET resembles its more sophisticated brethren in that the users are capable of working by themselves when not accessing the central peripherals. In an ordinary MP/M system, the additional users have to share the same CPU and memory system as well as the peripherals.

A CP/NET with only one shared MP/M server will display many desirable network features and lack some others such as a high speed communication system (communication is by way of ordinary I/O ports) or a sophisticated error-detection and correction capability. It can be favorably compared to a multi-processor system, since the users operate independently when not accessing the host system's facilities.

More network features appear when more than one of the workstations is equipped with an MP/M operating system rather than ordinary CP/M. Two or more such installations can access each others' peripherals, while communication between one MP/M and one CP/M station is more of a one-way operation. However, the communication in either case is at the inherently slow speed of an I/O serial port, and you might have to write or alter part of the software to have the kind of communication you really want.

## How it Works

Knowing CP/NET's terminology is important in understanding the system. Any MP/M equipped machine (or machines) rate the title of master and the CP/M workstations are called slaves. This fairly well describes their relationship as far as sharing facilities is concerned.

Essential elements of any CP/M system are the BIOS (I/O system) and BDOS (disk operating system.) When we graduate to MP/M we find that the BIOS is replaced by an XIOS (eXtended I/O) to handle multiple users, and that the BDOS is augmented by an "eXtended" XBDOS. This is the part that handles the time sharing chores. Figure 1 shows the relationship of these elements to system memory and the rest of the MP/M system. The configuration shown here would permit several terminals to share the MP/M-equipped computer. An MP/M system would normally share a single computer with several terminals.

CP/NET allows the slave users to be complete computers rather than simply terminals—thus, they are spared from having to all share the same CPU. The CP/NET operating system is a logical extension of the elements just discussed. Figure 2 shows the added elements and their relative position in the CP/M system. One of these new elements is

| XIOS                 |

|----------------------|

| XDOS                 |

| BDOS                 |

| MP/M<br>program area |

| BIOS (CP/M)          |  |

|----------------------|--|

| BDOS (CP/M)          |  |

| <br>SNIOS (NET)      |  |

| NDOS (NET)           |  |

| CP/M<br>program area |  |

Figure 1

Figure 2

the NDOS, or network system; another, the SNIOS is the slave I/O software.

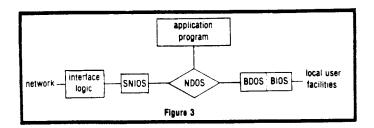

Notice now that the application program communicates directly with the NDOS; this is shown in flowchart form in Figure 3. The NDOS "decides" whether a particualr system call should be routed to the resident BDOS (as it ordinarily would be) or to the network, via the SNIOS. If the user has addressed one of his local peripherals, the I/O is handled by his internal CP/M system. If he has addressed a remote device, the I/O is routed to the network and thus to its ultimate destination. The slave user operates independently of the MP/M master except when accessing its peripherals.

# Using CP/NET

If you're familiar with CP/M you already know about the software linkage of "physical" and "logical" devices; these include the CON: or console, and the LST: or printer, among others. You also have available, in CP/M, several disk drive assignments. These various devices can be reassigned (within limits) by commands from the console.

CP/NET extends this capability. In CP/NET you can reassign some of the master's devices in a similar way. For example, NETWORK H: = C:(01) assigns disk drive H: of the master for use as drive C: by user number 1. Drive H: might be a single floppy or a segment of a shared hard disk. Similarly, a printer driven (served) by the master can be assigned to be the LST: device of one or more users. Following these assignments the user simply calls for drive C: or LST: just as he would if they were a physical part of his own installation. In a moment we'll look at how this is actually handled by the software.

The access of a master facility may not be instantaneous, because of the sharing that might be taking place. These delays, which hopefully will not be excessive, are handled by a "queuing" arrangement in the master's network software. User requests line up and wait their turn, if necessary.

# Implementation

There is some software modification to be made whenever a new CP/NET is placed in service. User and device assignments have to be made, to name the most important task. These assignments are entered into the software and become part of status tables. These tables have to be accessed by the individual user operating systems, to guide the routing of communication from one point to another.

Another important software task is the automatic

construction of "messages," within which the actual data or command (being transmitted from-here-to-there) is only one section. The source and destination addresses and some other control information are also appended. Figure 4 outlines a typical CP/NET message. Remember that you don't have to put this message together-the system does it for you. The real "data," which may be just a CP/M command line, is all that the user has to provide.

You might also wish to have some sort of customized hardware interface at each machine to permit the use of a communication protocol other than what is a part of your "normal" I/O ports. None of this should be very terrifying to experienced persons, but neither can the installation be considered just a "plug it in, turn it on" kind of operation.

| Format<br>Code | Destination<br>Address | Source<br>Address | Function<br>Code | Data<br>Length | Data |   |

|----------------|------------------------|-------------------|------------------|----------------|------|---|

| 1              | !                      |                   | 1                |                | 1    | ٠ |

Figure 4

### **Evaluation**

I must confess to having never used either MP/M or CP/NET, so this report is based on information released by Digital Research as well as reports found in other publications. It has been reported by others that implementing MP/M, either as a timesharing system or as part of CP/NET, is not a trivial task.

Based on my own experience with CP/M, and the general reputation of Digital's products, I would expect the system to be all that is claimed, and perhaps more. One expectations would be that current revisions might differ from, and be superior to, the original release. The price is attractive. I would expect that any CP/M compatible software would work with either MP/M or the network, which could be a valuable asset if you are already using such software.

My best guess is that "network" is stretching the term a bit if you compare this system to some of the more expensive ones such as Ethernet, but that it is a worthwhile compromise for the small-budget user of desktop computers. Because of rapid developments in networking technology, too, some of my source material might be obsolete by the time this column is printed. To be on the safe side, if you are interested, please research the matter in detail and make your own evaluation of whatever version is currently available.

For more information on MP/M and CP/NET, contact Digital Research Inc., Pacific Grove, CA 93950.

# Build a High-Resolution S-100 Graphics Board

Part Three: Construction

by Lance Rose, Technical Editor

In the first two parts of this series, we described what is needed to display a video image, and discussed the present circuit in depth-now it's time to get down to the actual construction details.

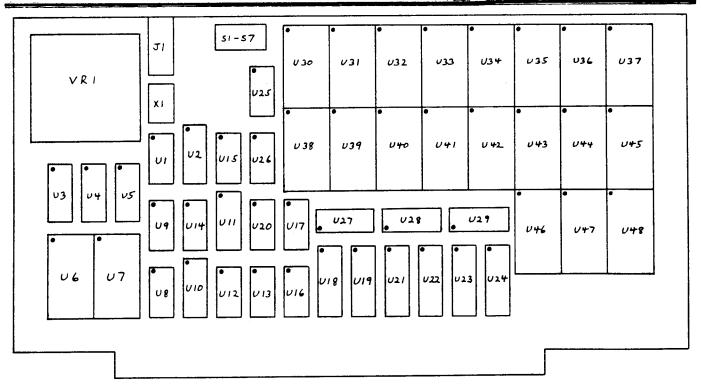

Figure 1 shows a photograph of the front side of the graphics board. Figure 2 shows a view of the back side which should help suggest some wire routings. These are not all that critical and if you prefer a different routing, go ahead and use it. Figure 3 is a drawing of the front side of the circuit board identifying each of the ICs on it along with the pin #1 locations.

The first obvious thing is that there are plenty of chips to find a place for, so there is no wasted space. Although the layout shown here is not the only possible one, I did experiment with several other variations and this one came out on top. The rationale behind the layout is as follows: The state ROMs and clock oscillator are all located near each other to minimize long connections. Most of the small LSTTL chips are also placed to minimize long connections and reduce clutter. The crystal is mounted near the top of the board to facilitate changing. Although this probably won't be a factor for you, during development I tried a couple of different crystals and wanted to be able to access it easily. Also, the crystal is mounted in a piece of socket cut from a DIP wire-wrap socket. This can be done with a small hacksaw or coping saw. Alternatively, you can solder it in if you're sure you won't have to change it. Personally, I am a fan of flexibility.

The DIP switch for address selection is also at the top of the board where it can be reached when the board is in the card cage. Once again, if you know you'll be setting the switches once and never again, you can move it down. You can even go further and eliminate the switch and wire wrap the inputs to the open-collector NOR gates to either +5V or ground. It saves one IC position but makes changing the address a bit of work.

All the bus interface chips are mounted near the bottom

of the board (near the bus, naturally). The address decoders and some of the other chips are in something of a compromise location. Since the RAM chips take up a lot of space, choosing a layout for them took quite a while. I tried layouts with the 24-pin sockets in a horizontal position but they didn't work out as efficiently.

If you have had some experience in board layout or just want to strike out on your own, by all means do so. There may be other layouts that are a hair better but I think most of you will be quite satisfied with this one.

You can see that the TO-3 type regulator takes up some room, but I'm a believer in adequate power supplies. I wouldn't feel good about using only a single TO-220 5-volt regulator even though on paper it has the same current capacity as the larger metal one. And two of the TO-220s take up as much space as one of the TO-3s when you include heat sinks for them, so....

The complete parts lists for the board is found in Table 1. As I stated in Part I of this series, you should be able to buy all the parts for around \$200, or even a bit less since the price of 6116 RAM chips has come down a little since I bought mine. If you were to try using soldertail sockets instead of wire-wrap and solder all the connections, the price would be even lower. However, being conservative, I wouldn't recommend that approach.

The basis of any layout you choose is, of course, the prototype board itself. There are a number of these to choose from. Some have pre-etched traces for power and ground, some have one pre-etched pad per hole, some have only an area for a voltage regulator (usually a TO-220) and some have nothing at all but the holes. The problem with any of those that have traces or pads laid out on them is that most of them assume you'll be using only 14 and 16-pin IC packages. Designs with a lot of 24-pin sockets don't seem to be able to take as much advantage of these pre-etched prototype boards. The good thing about them is that they usually have heavy traces for running power and ground

connections.

I normally use the completely blank boards, not just because they are the least expensive but because they offer the most flexibility in layout. Using one of these does require that you pay due attention to providing adequate power and ground "busses". A single strand of 30 gauge wire-wrap wire is a bit marginal in my experience. All power and ground leads should be doubled if at all possible. Alternatively, you can use some heavier wire for the power and ground leads and connect all the sockets to these busses with short lengths of 30-gauge wire. This approach is probably the best but requires more soldering, at least until you get the power and ground leads laid out. If you choose to distribute power and ground with wire-wrap wire, try to lay them out in a grid pattern to approximate a ground plane.

Another thing to watch is bypass capacitors. Be sure to use enough here. There are a lot of high-frequency signals running around, and one bypass cap per chip is not too much. This can be stretched a little in the RAM portion of the board since CMOS is more tolerant of noise. The RAM chips are crammed together pretty tightly and you might not be able to fit one in for each chip.

Before beginning the actual construction, let me warn you about the 24-pin sockets. Some brands are sized such that they can be placed side-by-side on a board with no blank rows of holes between them. Others require a small gap. You'll have to obtain the former kind in order to get everything to fit on this board. I got mine from Jameco, but I'm sure they are available from other sources as well. These particular ones have a "CA" stamped on the top of the socket. I don't know if this is the brand name or not, but if you order sockets remotely, be sure to ask for ones that will fit side-by-side. This only applies to the 24-pin sockets. With the others, there is always at least one row's spacing between them.

As a general procedure, I think it's best to begin by mounting the voltage regulator and tantalum electrolytics along with the connections to the S-100 8-volt and ground fingers. At the same time, you can do any other mechanical work necessary with a drill or file. The RCA phono jack shown here is mounted on a small L-bracket that has been drilled out to size. If you use a different type of connecter, do the appropriate work here so that when you get the sockets on the board you won't have to be drilling, sawing,

filing and sanding around them.

With a hefty TO-3 regulator you can afford to use one of the low-profile heat sinks. This will make it easier to get the finished board into your card cage. Once this is done, you can plug the board in and check out the regulator for proper voltage.

Following this, my own habit is to place all the sockets on the board and fasten them down by connecting the power and ground leads to them. At the same time I solder in the bypass caps. Powering up at this point will detect any shorted caps and it will be easier to find them without all the signal leads running around the board.

Perhaps I ought to say a word or two about color coding. I've seen projects built with only a single color of wire-wrap wire but debugging has to be more difficult that way. Even if all you have nearby is a Radio Shack store, you can still get 4 different colors - red, blue, yellow and white. If you're willing to mail order, you can get about another 4 or 5 colors. That may be going overboard. I usually use red for power supply, blue for ground, yellow for address lines and white for data and signal lines (actually five colors would be just right). This is just a personal preference on my part and if you would rather use all one color, by all means go ahead. As long as you can find your way around the board, that's all that matters.

After all the sockets are located on the board you can go ahead and start connecting the signal leads. The suggested order of wiring is as follows.

First wire the oscillator circuit, which includes the 7404, the crystal, and the necessary resistors and capacitor. You can then power up and check for oscillation. You should be able to detect this with a reasonably good scope or logic probe. Once oscillation is verified, the next section to wire is the state machine. This includes the 2732 EPROMs, all the 74LS193 counters, and two of the 74LS393s—U8 and U9, and the 74LS174.

If you are going to program your own EPROMs, the program listing in Figure 5 is the one to use. It requires the use of either Digital Research's MAC® macro assembler or a recent version of Microsoft's M80 assembler. If you don't have either one of these or can't get access to one, you can either rewrite the program in BASIC or order a set of ROMs from The Computer Journal. The price is \$25 per pair preprogrammed. If you have the facilities for programming and would like a machine-readable copy of the program, we

can provide one on 8" single density CP/M for \$15. This also includes the test program and sample use program whose listings appear in Figures 6 and 7 here. We may also be able to provide some 5.25" formats but you'll have to check with us and see if it's one that we can make.

Once this is done and you have either programmed your own EPROMs or obtained them from us, you can plug the board in and look at the outputs of the 74LS174 to see if the timing is about what you would expect. This would mean blanking and sync outputs at approximately the horizontal sweep frequency and RAM counter reset (pin 15) once every 1/60 second. If these outputs look about right, the state machine is probably working fine.

Next go ahead and wire up the 74LS165 shift register and any necessary gates associated with it. Wire the transistor and the rest of the output circuit as well. Although I used a 2N5450 transistor in my version, it was mostly because I happened to have a bunch of them in my junk box. Almost any small-signal transistor with a decent gain and bandwidth should work, so try using what you have handy.

You can now connect the board to your video monitor for further troubleshooting. With the power on, the video screen should display a uniform bright raster with no tearing or lack of synchronization. If you can't get the image to lock in with the monitor's horizontal and vertical hold controls, something is out of whack. Try looking at the composite video output with an oscilloscope. The waveform should appear much as in Figure 2 in Part I of this series. Check both voltage levels and timing. The signal level can be off quite a bit and still work by adjusting the brightness and contrast accordingly, but the timing should be very close. If it isn't, stop and check all connections in the timing

circuit U3-U5 as well as the state ROM address counters U8 and U9. Also check the dot clock and byte clock outputs for proper frequency.

Once you get a display that will lock in on the screen, go ahead and, using a clip lead, ground each of the parallel data inputs to the 74LS165 in turn. This should result in a series of thin, dark vertical lines in the bright field. Grounding two adjacent data inputs will produce wider dark lines. If this is what you get, so far so good.

Next try wiring up the local RAM address counters U16 and U17, buffers U18 and U19 and any necessary gates that go with them. Wire up at least one of the 6116 sockets, preferably one adjoining U18 or U19. This will let you display information from the video RAM without having to have all the sockets wired. You should also wire up the address decoders U27, U28 and U29a and U20d, but only connect the chip select line for the one RAM socket you have in at the present. You'll also need U14b and U12d (you can leave pin 9 on the latter open for now).

On powering up you should get an all-white (green) display except for a small area where the single 6116 is. In that area the screen should show random dots both on and off. In all likelihood, the pattern will be somewhat regular and probably look like alternating white and black bars about 8 dots wide each. This is simply due to the power-up characteristics of the 6116 and has no other significance. There will be a few random areas anyway. If you don't get alternating bands, don't worry. The important thing is to identify at least a few features attributable to random bits.

If things are working here, you're over the hump. Go ahead and make the connections for all the bus interface logic. This means wire everything else except the remaining

Figure 3: Component layout for board.

RAM chips. Also, put in the DIP switch if you're going to use one. If you like you can place it in a socket, as I did. Double check all but the remaining RAM connections and you're ready for an actual test.

Plug the board into your bus and power up. Of course if your machine won't operate at this point, you have a problem. Most likely you made a connection to a wrong bus pin or accidentally grounded a bus line or something of that nature. I have found that about 90% of all errors in prototype circuits can be found by visual inspection, checking the wiring against the schematic. Another thing you should be checking on a regular basis here is the output from the regulator. If it is more than about a quarter of a volt off, you probably should try another regulator.

After you get the board in and the machine running, the easiest way to check the board out is from BASIC. The general procedure for writing a byte to the video RAM is as follows:(Assume the board is addressed at locations 100, 101, 102 decimal)

- (1) Output the low byte of the desired video RAM address to port 100.

- (2) Output the high byte of the desired video RAM address to port 101.

- (3) Output the desired data byte to be placed in video RAM to port 102.

You should be able to tell what addresses are active by which RAM socket you wired up. Outputting a byte of 0 will make a dark line 8 dots wide appear at that location. A byte of 255 will make a bright line of the same size. Intermediate values will turn on or off all other possible combinations. If it doesn't appear to work right away here, double check to see that the single RAM chip you have wired up is at the address you think it is. If you're not sure, you can always go ahead and wire up all the rest of the RAM sockets and install the chips. However, that's a lot of connections and if you know you already have a working board and just have to mechanically run the wires, it seems to be psychologically easier.

If you just can't get any effect from trying to write into the video RAM, you'll need a logic probe to do some tracing. Check for the WE\* pulse on pin 21 of the RAM during the write operation. If you think it will help, you can disable the arbitration circuitry and allow constant access to the video RAM from the bus by temporarily removing the wires from pins 10 and 12 of U10 and grounding them. This should constantly select the bus address latches as the address generators for the RAM chips. Just don't forget to change this back after you find the problem. Make sure that U18 and U19 are not being enabled at the same time as U21 and U22. Check for the usual things like bent-under pins on

|                         | non of commission                                                                                                                |

|-------------------------|----------------------------------------------------------------------------------------------------------------------------------|

| C1                      | 220 pf ceramic disk<br>470 pf ceramic disk                                                                                       |

| C2                      | 4.7 uf/25V tantalum electrolytic                                                                                                 |

| C3,C4<br>C5-Cn          | 0.1 uf ceramic disk (bypass)                                                                                                     |

| C5-Cn                   | U.1 UI CETAMIC GISK (Dypass)                                                                                                     |

| J1                      | RCA phono jack                                                                                                                   |

| l * -                   | nai prono year                                                                                                                   |

| Q1                      | 2N5450 or equivalent                                                                                                             |

| _                       |                                                                                                                                  |

| R1,R2                   | 470 ohm, 1/4 watt                                                                                                                |

| R3                      | 100 ohm, 1/4 watt                                                                                                                |

| R4                      | 220 ohm, 1/4 watt                                                                                                                |

|                         | 150 ohm, 1/4 watt                                                                                                                |

| R7-R14                  | 2.2 kohm, 1/4 watt                                                                                                               |

|                         | 9                                                                                                                                |

| S1- <b>S</b> 7          | 7-position DIP switch                                                                                                            |

| บา                      | 7404 hex inverter                                                                                                                |

| υ2 <b>-υ</b> 5          | 7404 hex inverter 74LS193 presettable binary counter 2732 4Kx8 EPROM 74LS393 dual binary counter                                 |

| U6,U7                   | 2732 4Kx8 EPROM                                                                                                                  |

| UB.U9.U16.U17           | 74LS393 dual binary counter                                                                                                      |

| U10                     | 74LS174 hex D flip-flop                                                                                                          |

| U1 1                    | 74LS165 shift register                                                                                                           |

| U12                     | 74LS02 quad NOR gate                                                                                                             |

| U13                     | 74LS32 quad OR gate                                                                                                              |

| U14                     | 74LS08 quad AND gate                                                                                                             |

| U15                     | 7406 hex driver, open collector                                                                                                  |

| U18,U19,U23,U24         | 74LS244 octal buffer                                                                                                             |

|                         |                                                                                                                                  |

| <b>U21,</b> U2 <b>2</b> | 74LSOU quad NAND gate 74LS174 Octal D flip-flop, 3-state 74LS186 quad exclusive NOR, open collector 74LS188 one of eight decoder |

| U25,U2 <b>6</b>         | 74LS266 quad exclusive NOR, open collector                                                                                       |

| U27,U28                 | 74L5138 one of eight decoder                                                                                                     |

| 029                     | /4LS139 dual one of four decoder                                                                                                 |

| U30-U48                 | 6116-4 2Kx8 CMOS RAM                                                                                                             |

| VR1                     | 7805K 5 volt regulator, TO-3                                                                                                     |

| хı                      | 16 MHz crystal                                                                                                                   |

| ,                       |                                                                                                                                  |

| Ī                       | Table 1: Parts List                                                                                                              |

chips, bad chips (very unlikely) or wiring errors (much more likely). It's hard to give specific instructions here since there are so many variations. As I said above, most of my own errors have been due to accidentally leaving a connection out or making it to the wrong pin. When you're staring at about a thousand pins upside down and backwards, it's not too hard to do.

After debugging the write portion, try reading the byte back. You can skip steps 1 and 2 above if you're accessing the same location. For step 3, input a byte from port 102 and see if it's the same as what you output. If not, use similar debugging techniques on the read portion of the bus interface logic. Note here that you can do either 1 or 2 above without the other. You only need to change the portion of the address that is different from the last address accessed.

The final step, once the board is working with a single chip, is to add the other RAMs. It just takes some time. With all the RAM chips plugged in, you're ready for final checkout. A simple test program in Microsoft BASIC is shown in Figure 6. It writes random bytes to random screen locations and then attempts to read them back. Make sure the DIP switch on the board is set for 100 decimal (64H) or else change the port numbers in the test program to coincide with what you have the switches set for. If an error is detected, the program reports it. When the program is running the screen should display a speckled random pattern that changes slowly, one speckle at a time. No hash should be seen in the display at all. If there is hash, suspect the interlock circuit that is supposed to keep the processor waiting during scan lines. Also check the wait state circuitry on the CPU board to make sure it's functioning properly. Most newer memories don't require any wait states so yours

Figure 5: Program for T.V. signal ROMs. :Equalizing pulses MOPLSE-1 LIME/2-EOPLSE-1 AND OFFH 2732 ROM program to generate TV waveforms Used for 1/0-mapped graphics board Version of 2/3/64EOPLSE-1 :Balf equalizing line LINE/2-EOPLSE-1 AND SPFH :Generate blanking level

:Generate sync level

:Count up RAM pointer with dot clock

:Generate wait state

:Maintain wait state and disable MMKITE

:Keer wait, MMKITE disabled, use RAM pointer

:Reset RAM pointer

:Scan lines in blanked top of frame

:Scan lines in view area

:Dots in line

:Dots in horizontal sync pulse

:Dots in left border

:Dots in view area

:Dots in right border

:Dots in right border

:Dots in equalizing pulse

:Dots to finish current

:Dots to funish current

:Dots to turn off MMRITE

:Dots to change multiplexer inputs BLANK SYNC COUNT WAIT DISABL High byte ROM EQU EQU EQU :Blanked lines at top of first field REPT LOX'L RESET RESET

TCP

VERT

LINE

HSYNC

LEFT

HOR12

RIGHT

EOPLSE

FINISH

WRTOPF

SWITCH ;Visible lines in first field PLANK+SYNC BLANK+SYNC ;VI BLANK HAIT BLANK+HAIT BLANK+DISABI. BLANK+LOCI. LOCI+(HORIZ-1)/256 BLANK+DISABI. BLANK VERT/2-1 BLANK+SYNC+COUNT BLANK BLANK+DISABI BLANK+DISABI BLANK+DISABI BLANK+DISABL BLANK+DISABL BLANK+DISABL BLANK+DISABL BLANK+DISABL :Blanked lines at top of first field REPT DF DB DP DB DB DB DB ENDM DB DB ENDM BLANK+SYNC :Blanked half line BLANK+(LINE/2-HSYNC-1)/256 DB DE :Visible lines in first field VERT/2 (Visible line HSYMC-1 LETT-PINISH-WRTOPP-SWITCH-1 FINISH-1 WRTOFF-1 REPT DF DB FP DB CB DB UF DB ENDM :Equalizing pulses REPT DB ENDM WRTOFF-1 SWITCH-1 HORIZ-1 AND ØFPH SWITCH-1 FIGHT-SWITCH-1 f ;Vertical retrace

BLANF+SYNC+(LINE/2-HSYNC-1)/256

BLANK REPT DR ENDM HSYNC+1 :Flanked half line LINE/2-HSYNC-1 AND ØFFH DP DF ;Equalizing pulses REPT BLANK+SYNC ELANK+(LINE/2-EOPLSE-1)/256 :Equalizing rulses REPT EOPLSE-1 LINE/2-EOFLSE-1 AND BEFH RLANK+SYNC :Full equalizing line BLANE+RESET+(LINE-EQPLSE-1)/256 EB DF 6 (Vertical retrace Line/1-HSYNC-1 AND #FFH newword TOP/2 BLANK+SYNC FLANK BLANK ELANK ELANK REPT :Blanked lines at top of second field :(Includes blanked half line) RE PT :Equalizing pulses EOPLSE-1 11NE/2-EOPLSE-1 AND ØFFE DR ENDM FOPLSE-1 :Full equalizing line LINE-FOFLSE-1 AND BEFH VERT/2 ;Visible lines in second field BLAM:+SYNC+COUNT ELAN:+SYNC+COUNT BLAN:+GEART BLAN:+GEART BLAN:+GEART ELAN:+GEART ELAN:+GEART BLAN:+GEART ELAN:+GEART BLAN:+GEART BLAN:+GEART BLAN:+GEART BLAN:+GEART BLAN: :Flanked lines at top of second field DB DB DB ENDM :Equalizing pulses REPT V:Visible lines in second field REP1 VERT//

HEYN -1

LEFT-FINISH-WRTOFF-SWITCH-1

FINISH-I

WFTOFF-1

SWITCH-1

HORIZ-1 AND ØFFE

SWITCH-1

RIGHT-SWITCH-1 BLANE+SYNC BLANE+(LINE/2-EOPLSE-1)/256 E ;Vertical retrace

BLANF+SYNC+(LINE,2-HSYNC-1)/256

ELANK REPT DH DB ENDM DP DB DB ENDM :Equalizing pulses BLANF+SYNC BLANF+(LINE/2-EOPLSE-1)/256 ;Equalizing pulses DE DB ENDM DB DE EOPLSE-1 LIME/2-EOPLSE-1 AND OFFE DB EINDM ELANF+SYNC :Half equalizing line BLANK+RESE1+(LINE/2-EQPLSF-1)/256 ; Vertical retrace LINE/2-HSYNC-1 AND #FFR HSYNC-1 END

may not be working and you won't have known it. If every byte comes back an error, something is wrong in the read portion of the bus interface logic. Check wiring. If only occasional errors occur, check for good grounding and power connections. Also, make sure there are enough 0.1uf bypass caps.

When the board passes the GTEST program, you can then try out the sample plotting program included here in Figure 7, also in Microsoft BASIC (but easily convertible to another BASIC). A screen menu lets you choose a variety of functions to test the board. The scale is assumed to be linear in both directions and the left, right, upper and lower limits

can be changed with the "Set Limits" option. After that you can set an individual point, draw a straight line, an arc or a sine curve (arguments in degrees).

The program is designed mostly for fooling around and as an example of how to use the facilities of the graphics board. The painful slowness of BASIC is amply evident here. Any truly useful graphics programs simply must be written in assembly language to operate with any kind of reasonable speed. Compiled BASIC or FORTRAN are improvements but still not as good as assembly. If you aren't doing at least some assembly language programming yet, this may be the impetus you need.

#### Figure 6: BASIC test program.

# Figure 7: BASIC program to draw some shapes with the board.

If you have gone this far and actually built the board, you probably had some ideas of what you wanted to use it for. Some of the things I wanted to do were to plot 3dimensional figures, plot orbital data from my astronomy programs, generate Fourier waveforms and use it to display alphanumeric data in any one of a number of character fonts. Since the board is programmable on the dot level, you can make up characters in any shape you like (APL, Chinese, Arabic, Hebrew, Greek, etc.) You can do proportional spacing. You can plot in rectangular or polar coordinates. Its uses are limited only by your imagination.

Although this concludes the series of construction articles on this board, there may be other articles on specific applications in the future if interest warrants it. We'd like to hear your views on it. If you build the board, we'd also like to hear your difficulties, if any, and your reactions to the completed product.

# MicroMotion

# **MasterFORTH**

It's here — the next generation of MicroMotion Forth.

- Meets all provisions, extensions and experimental proposals of the FORTH-83 International Standard.

- Uses the host operating system file structure (APPLE DOS 3.3 & CP/M 2.x).

- Built-in micro-assembler with numeric local labels.

- A full screen editor is provided which includes 16 x 64 format, can push & pop more than one line, user definable controls, upper/lower case keyboard entry, A COPY utility moves screens within & between lines, line stack, redefinable control keys, and search & replace commands.

- Includes all file primitives described in Kernigan and Plauger's Software Tools.

- The input and output streams are fully redirectable.

- The editor, assembler and screen copy utilities are provided as relocatable object modules. They are brought into the dictionary on demand and may be released with a single command

- Many key nucleus commands are vectored. Error handling, number parsing, keyboard translation and so on can be redefined as needed by user programs. They are automatically returned to their previous definitions when the program is forgotten.

- The string-handling package is the finest and most complete available.

- A listing of the nucleus is provided as part of the documentation.

- The language implementation exactly matches the one described in <u>FORTH TOOLS</u>, by Anderson & Tracy. This 200 page tutorial and reference manual is included with MasterFORTH

- Floating Point & HIRES options available.

- Available for APPLE II/II+/IIe & CP/M 2.x users.

- MasterFORTH \$100.00. FP & HIRES -\$40.00 each (less 25% for FP & HIRES).

- Publications

- FORTH TOOLS \$20.00

- 83 International Standard \$15.00

- FORTH-83 Source Listing 6502, 8080, 8086 -\$20.00 each

7 Business Park Drive • P.O. Box 699 • Branford, CT 06405 • (203) 488-6603 • TWX: (910) 997-0684

Easy Link Mail Box: 62537580 • CompuServe: 71346, 1070

U.S. and Canadian Distributor inquiries welcomed.

# SYSTEM INTEGRATION

Part Three: CP/M 3.0

by Bill Kibler

In the first part of this series, we discussed factors to keep in mind when choosing components for system integration. In part two we looked at how SDSystems V.ersafloppy II was set up to run CP/M 2.2. I hope that most readers will have at least a 2.2 system running at this stage. If you have not yet used a 2.2 system, a complete reading of this article and other books will be necessary before considering CP/M 3.0. To help the novice and weekend hacker, let's first review what a 2.2 system does.

# **CP/M 2.2**

CP/M is the interface between the hardware of your individual system and the generic types of software you will run. This program, known as an operating system, provides standard interfaces in two directions, one to transient programs and one to fixed hardware. CP/M advanced through many variations and stabilized for some time at version 2.2. This version is intended to run on an 8080 or Z80 CPU with 64K of memory, using fixed peripherals for I/O. An assembler, a debugger, an editor, and several other utilities are provided with the purchase of CP/M. This entire operating system makes it possible to change, modify, and generate new operating systems, in addition to running purchased programs with few problems.

The ins and outs of 2.2 are well known, and for those looking for more knowledge, your local computer store has many books on the subject. 2.2's structure is extremely straightforward. The relationship between the three modules that make up the program are fairly easy to explain. The CCP is the command processor and handles communications with the operator while in the system mode (not running any generic programs). The BDOS (basic disk operating system) is the next module, and does most of the work. It works with running programs by the use of function calls. The function calls are separate routines that together form the BDOS and allow canned programs to operate on different hardware. The BDOS takes a function call and talks to the next module, the BIOS (basic in/out system) as many times as necessary to make the hardware perform the requested function.

2.2 has been around for so long now that other products are available that can enhance or replace all or portions of CP/M. With the books and software base available, this operating system has little equal and allows me to recommend it without question as the choice of hackers. However, like most manufacturers, DRI (Digital Research Inc.) felt that an improved version of CP/M that incorporated most of the enhancements would allow them to take back control of their product. An improved version would also present an opportunity to work out the

incompatibilities between 2.2 and DRI's multiuser operating system, MP/M. The cost of memory has decreased in quantum leaps, reducing the expense of having more than 64K, and a system was needed that could make use of this cheap memory. So CP/M 3.0 was born.

# **CP/M 3.0**

CP/M 3.0 or "PLUS," as it is sometimes called, is little different from 2.2. It is still the operating interface between the hardware and software, but with some new wrinkles. Memory can now be in multiple banks, outputs from programs can be changed or redirected, additions to the operating system can be created and tacked on, there are help programs and command line editing, and lastly, the system is supposed to be faster. What has been lost is a simple BIOS program and a lot of disk space. Although the gains may seem to outweigh the losses, closer investigation is needed.

To utilize CP/M 3.0 more fully you will need more than one bank of memory. In the non-banked mode most of the enhancements are lost, as well as part of the transient program area (TPA). Current programs require up to 56K of temporary program RAM to run, and the non-banked TPA of 50 or 51K may not work. Once the BIOS has been generated for banked operation the TPA expands to over 60K, which can be more than most 2.2 versions. The extra banks contain the larger BDOS, a copy of the CCP program (3.0 CCP is a transient program and not resident like 2.2), and data buffers. Higher operating speeds are possible for programs that use high disk access by locating the most highly and currently used sectors in the disk buffers (other banks). These buffers are assigned and managed by the BDOS and are not controlled in any way by the operator.

Inputs and outputs are normally assigned through fixed BIOS definitions or routines. In 3.0, tables of I/O types and requirements are maintained, which allow the system configuration to be changed without rewritting the BIOS. This operator freedom of choice is made at the expense of memory (banked RAM) and speed (the whole table is scanned for each output of a character). 2.2 has an I/O byte that has now been expanded to several bytes to take into consideration the different possible ways of redirecting the data flow. A new program type, the RSX module, has been added. This program technique is helpful for those who want to add some special function that the BDOS doesn't currently support. The new module is put below the BDOS and the inputs to the BDOS are redirected through it. In 2.2 this was not possible except for enhancements to the BIOS routines as is done in RAM DRIVE modifications.

The banked version allows the command line to be edited