Small Scale Computing Since 1983

Supporting the Trailing Edge of Technology

# The Computer Journal

**Issue** Number 77

January/February 1996

US \$4.00

| Reader to Reader     | GIDE News and more      |

|----------------------|-------------------------|

| Real Computing       | 32-bit OS Reviews       |

| Mr.Kaypro            | Kaypro External Video   |

| The European Beat    |                         |

| Hands on with PLD's  | Mem Decoder/Clock Gen   |

| Dr. S-100            | S-100 Memory Management |

| Center Fold          | CPU280                  |

| The First TRS-80     |                         |

| Small System Support |                         |

| Program This!        | Z80 SIO                 |

| Morrow MD-3P         | Repair                  |

| Computer Corner      | Forth Day 1995          |

ISSN # 0748-9331

Hands-on Hardware and Software

# Cross-Assemblers as low as \$50.00 Simulators as low as \$100.00 Cross-Disassemblers as low at 100.00 Developer Packages as low as \$200.00(a \$50.00 Savings)

**A New Project**

of macro Cross-assemblers are easy to use and full featured, conditional assembly and unlimited include files.

Get it To Market—FAST

alt until the hardware is finished to debug your software. Our program logic before the hardware is built. No Source!

High has shown up in the firmware, and you can't find the original segrant. Our line of disassemblers can help you re-create the assembly language source.

Set To Go

toper package and the next time your boss says "Get to work.", by for anything.

Quality Solutions

s been providing quality solutions for microprocessor

**BROAD RANGE OF SUPPORT**

ently we support the following microprocessor families (with fore in development):

800

ACA 1802.05 Motorola 6801 Motorola 6809 Intel 8080.85 Motorola 68000.8

Intel 8051 Intel 8096 Motorola 68HC11 Motorola 6805 MOS Tech 6502 WDC 65C02 Zilog Z80 NSC 800 Intel 80C196

So What Are You Waiting For? Call us:

**PseudoCorp** Professional Development Products Group 921 Country Club Road, Suite 200

Eugene, OR 97401 (\$63, 683-9173 FAX: (503) 683-9186 BBS: (503) 683-9076

# Hiding in Plain Sight...

Some of the most interesting, challenging programming is being done outside the prevailing paradigms. It's been this way for years, and some companies regard its SPEED, COMPACTNESS, EFFICIENCY and VERSATILITY as their private trade-secret weapon.

It has penetrated most of the FORTUNE 500, it's a veteran in AEROSPACE, it's in SPARC WORKSTATIONS, and it's how "plug and play" is implemented in the newest Power PCs. In fact, it's lurking around a lot of corners.

It's FORTH, Surprised? Call now to subscribe\* and learn more about today's Forth.

Forth Dimensions 510-89-FORTH Fax: 510-535-1295

\*Ask for your free copy of "10 Ways to Simplify Programming"

# Kibler Electronics

Serving the Industrial Electronics Community since 1978

> Specializing In Hardware Design and Software Programming

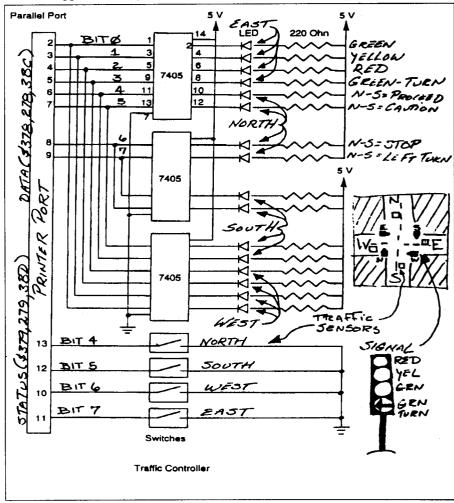

Previous Projects include: PLC tadder programming (15,000 lines) 8051 Remote I/O using MODBUS 6805 Instrumentation Controller 68000 Real Time Embedded Operations NETBIOS programming and Debugging Forth Projects and Development HTML Design and programming Articles, Training, and Documentation

> Bill Kibler Kibler Electronics P.O. Box 535 Lincoln, CA 95648-0535 (916) 645-1670

e-mail: kibler@psyber.com http://www.psyber.com/~kibler

# SAGE MICROSYSTEMS EAST

Selling and Supporting the Best in 8-Bit Software

Z3PLUS or NZCOM (now only \$20 each) ZSDOS/ZDDOS date stamping BDOS (\$30)

> ZCPR34 source code (\$15) BackGrounder-ii (\$20) ZMATE text editor (\$20) BDS C for Z-system (only \$30)

DSD: Dynamic Screen Debugger (\$50) 4DOS "zsystem" for MSDOS (\$65) ZMAC macro-assembler (\$45 with printed manual)

Kaypro DSDD and MSDOS 360K FORMATS ONLY Order by phone, mail, or modem and use

Check, VISA, or MasterCard. Please include \$3.00 shipping and Handling for each order.

# Sage Microsystems East

1435 Centre Street Newton Centre MA 02159-2469 (617) 965-3552 (voice 7PM to 11PM) (617) 965-7046 BBS

# **The Computer Journal**

Founder Art Carlson

Previous Publishers

Bill D. Kibler

Chris McEwen

Editor/Publisher

Dave Baldwin

Technical Consultant Bill D. Kibler

Contributing Editors

Herb Johnson

Charles Stafford

Brad Rodriguez

Ronald W. Anderson

Helmut Jungkunz

Frank Sergeant

Richard Rodman

The Computer Journal is published six times a year and mailed from The Computer Journal, P. O. Box 3900, Citrus Heights, CA 95611, (916) 722-4970.

Tilmann Reh

Opinions expressed in *The Computer Journal* are those of the respective authors and do not necessarily reflect those of the editorial staff or publisher.

Entire contents copyright © 1996 by *The Computer Journal* and respective authors. All rights reserved. Reproduction in any form prohibited without express written permission of the publisher.

Subscription rates within the US: \$24 one year (6 issues), \$44 two years (12 issues). Send subscription, renewals, address changes, or advertising inquires to: The Computer Journal, P.O. Box 3900, Citrus Heights, CA 95611-3900.

# **Registered Trademarks**

It is easy to get in the habit of using company trademarks as generic terms, but these trademarks are the property of the respective companies. It is important to acknowledge these trademarks as their property to acid their losing the rights and the term becoming public property. The following frequently used trademarks are acknowledged, and we apologize for any we have overlooked.

overlooked.

Apple II, II+, IIc, IIe, Lisa, Macintosh, ProDos;

Apple Computer Company. CP/M, DDT, ASM, STAT,

PIP; Digital Research. DateStamper, BackGrounder ii,

Dos Disk; Plu\*Perfect Systems. Clipper, Nantucket,

Nantucket, Inc. dBase, dBASE II, dBASE III, dBASE III

Plus, dBASE IV; Ashton-Tate, Inc. MBASIC, MS-DOS,

Windows, Word; MicroSoft. WordStar; MicroPro International. IBM-PC, XT, and AT, PC-DOS; IBM Corporation. Z80, Z280; Zilog Corporation. Turbo Pascal, Turbo

C, Paradox; Borland International. HD64180; Hitachi

America, Ltd. SB180; Micromint, Inc.

Where these and other terms are used in *The Computer Journal*, they are acknowledged to be the property of the respective companies even if not specifically acknowledged in each occurrence.

# TCJ The Computer Journal issue Number 77, January/February 1996

| Editor's Column                                                          |

|--------------------------------------------------------------------------|

| Reader to Reader3                                                        |

| Real Computing                                                           |

| Mr. Kaypro9 The last of the external video mods. By Charles B. Stafford  |

| The European Beat                                                        |

| Hands on with PLD's14 Clock generator and Memory Decoder By Robert Brown |

| Dr. S-100                                                                |

| Center Fold                                                              |

| The First TRS-80                                                         |

| Small System Support                                                     |

| Program This!                                                            |

| Morrow MD-3P Repair43 MD-3P repair details By Jay Huddleston             |

| Support Groups for the Classics46                                        |

| Back Issues48                                                            |

| The Computer Corner                                                      |

# **Editor's Column**

# And in this issue...

On my first issue, I'm little bit late. I decided that it was better to try to get a good issue out rather than a quick one. I'm sure you'll let me know if I did or didn't. Add that to some project deadlines that occured at the same time and here we are.

And since I'm rushing to get this to the printer tomorrow, I can't find my editor's soapbox. So all I have this time is some news.

The one thing this issue is missing is a Forth article. I hope our Forth authors will send me at least one for the next issue.

I was hoping to have an article by David McGlone of the Z-Letter in this issue. The story of what it took to make some of the CP/M software available should be interesting. Unfortunately, he was just too busy.

Herb Johnson may be taking a breather after #78 for the same reason, too much work to do. We'll see articles from him when he has time.

Also because Herb has become real busy, it looks like TCJ will become the US distributor for Tilmann Reh's GIDE board. There will be more about this in #78 because the details aren't finalized yet.

Dave Baldwin TCJ Editor

# **Events**

Trenton Computer Festival is scheduled for the weekend of April 20-21. It has a CP/M and Z-System conference.

1996 Rochester Forth Conference will be held June 19-22 in Toronto at Ryerson Polytechnic University. Conference info available on the Web at "http://maccs.dcss.mcmaster.ca/~ns/96roch.html" or from Elliott Chapin at 416-921-9560.

# **TCJ Phones and Internet Addresses**

The Computer Journal

(800) 424-8825 or (916) 722-4970

Email: tcj@psyber.com BBS: (916) 722-5799 FAX: (916) 722-7480

Dave Baldwin: dibald@netcom.com

WWW Home page: "http://www.psyber.com/~tcj"

This issue includes the first of the TCJ Reference Cards. This time it's the Z80/180 instruction set. It's put inside the Center Fold with a single staple and intended to pulled out and used. Each issue will include a TCJ Reference Card related to one or more of the articles in that issue.

There's been a lot of activity with GIDE since the last issue. Reader to Reader is filled GIDE news and Helmut has some more in in The European Beat.

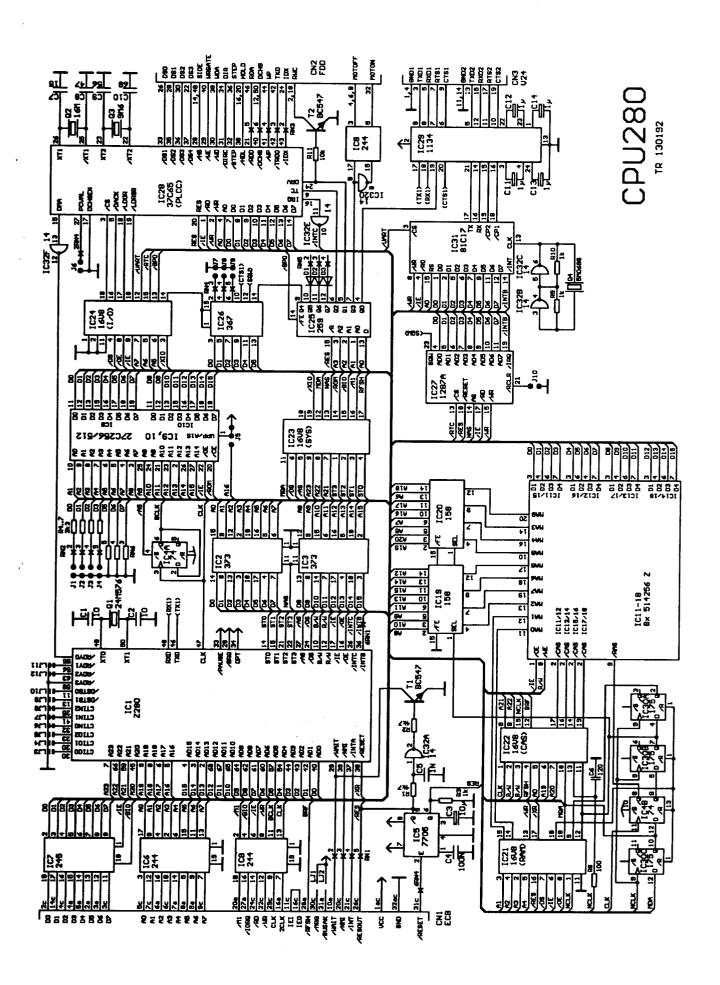

The Center Fold this is Tilmann Reh's CPU280. I wanted this to be an example of a modern CP/M system. However, now it's 'obselete' because Zilog decided to stop making the Z280 CPU. We finally publish the schematic for it along with the code for the PLD's.

Speaking of PLD's, Robert Brown (of Alta Engineering) wrote Hands on with PLD's for this issue. He gives examples of a clock generator and a memory decoder for a Z80. He shows how easy it is to decode odd size memory regions with a PLD. He has also uploaded files for building the Alta Engineering PLD programmer, a digital storage scope, and a Logic Analyzer with the PLD source files to the TCJ/DIBs BBS.

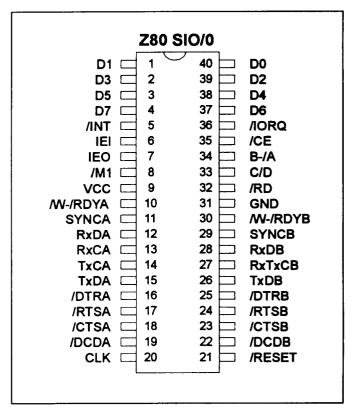

A new feature in this issue is **Program This!** This column will focus on a specific chip or device and provide enough info for you make it work. This time, I'm writing about the **Z80 SIO.** The article provides code samples for both polled and interrupt mode operation and complete source code for two different programs will be available on the TCJ Web and TCJ/DIBs BBS.

Gary Ratliff has an article about The First TRS-80, the Model 1 and tells about programming it in two different versions of Basic.

Chuck Stafford, Mr. Kaypro, is back with the last of the external video mods for the Kaypros and schematics for three different versions.

Our other regulars are here too. Rick Rodman has OS and programmer reviews in Real Computing. Ronald Anderson shows methods in 'C' for finding prime numbers in Small System Support. And Herb Johnson, Dr. S-100, talks about S-100 memory management.

# In The Next Issue:

Number 78 will include articles about a homebuilt TTL processor, a DIY 6502 circuit, and the 8031 along with all the regulars.

# READER to READER

# Letters and News All Readers MINI Articles

The letters this time are more like the GIDE News column. Read Helmut's article for even more. We also have a message about a new programmer's organization for CP/M software and a couple of help requests.

Hello Dave,

After having read the current TCJ issue #76, I have (as usual) some comments. But before I start commenting, there is another actual theme to talk about. Thanks very much for your message indicating that the Z280 is going out of production. When I previously asked my distributor, they always told me they'd inform me when any product I've ever bought there is cancelled. However, they didn't tell me, and still they can't explain how this could happen. But, fortunately, they have a current order which they will get in spring, and I can have some of those "last Z280 chips". Now I already ordered a few, to have spares for the CPU280 systems which are already in use. But I also would like to note that this is about the last possibility for getting a CPU280 system! If there is anybody out there who wants to take this chance, please leave me a note. If there are some orders, I will try to get more Z280's - however, they're too expensive to put many of them on stock just in case anyone wants a CPU280 later.

Now on to the comments on TCJ #76. In his column about XT's, Frank Sergeant also covers modern hard drives. Because there still are some questions, let me shortly explain the "difference" between IDE and the so-called EIDE. The truth is, there is \*no\* difference! If that sounds surprising, please think of the following details. As described earlier in my IDE article series, IDE uses an 8-bit sector

number register and a 16-bit cylinder register, while the head is contained in the lower four bits of the SDH register. This gives a maximum capacity of 65536 cylinders by 16 heads by 256 sectors by 512 bytes, aka 128 Gigabytes!

Now let's look at how PC's do hard disk accesses. Their ROM-BIOS masks the cylinder number to 10 bits and the sector number to 6 bits, since the very first hard disk controller was limited to those values. The resulting accessable capacity then is 1024 cylinders by 16 heads by 64 sectors by 512 bytes, which is 512 Megabytes. Now does this value sound familiar to you? Right, it's the so-called "IDE capacity limit", but it is not caused by the interface or the drive, it's just because the PCs ROM-BIOSs never stopped masking off those higher bits!

When it became obvious that 512 MB were not enough, the manufacturers simply blamed the drives and their interfaces, and created a "new" standard which would remove this restriction: EIDE. In fact, physically and logically EIDE is identical to IDE. The only thing that was changed was the bit-masking in the ROM-BIOS: socalled EIDE controllers (or capable PCs) simply don't mask off any bits from cylinder and sector registers. This is confirmed by the fact that you can mix-up either type of drive and "controller": it will always work perfectly. Just the old PC with its "IDE-controller" will be unable to access anything beyond the 1024x16x64 limit. It's only a question of software. For those "older" PCs there are drivers which replace the ROM-BIOS driver and don't mask any bits off, and with such a driver it's perfectly possible to completely use so-called EIDE drives on an old so-called IDE controller. (BTW, there are many older IDE drives which

have more than 1024 cylinders, and the drives itself were never limited to this value.)

This is just another case of willing disinformation in the PC business! (There are some more, like diskette capacities which are far less than would be (legally) possible, just because of IBM's thumbness!)

Another detail mentioned by Frank is LBA. LBA stands for "Logical Block Address(ing). Its meaning is rather simple: the sector number, cylinder, and head registers are logically combined to form a 28-bit absolute sector number. With LBA, you don't have to care about any drive's geometry, just access the sectors by their absolute number. Drives which are capable of LBA, indicate this by a status bit in the "Identify Drive" result. For each command, the desired mode (LBA or CHS, for Cylinder Head Sector) must be explicitly set.

I think LBA is an attempt to eliminate all those geometry emulations which were caused by some unflexible BIOSs (see? again a PC software problem), and it also provides similar access as with SCSI drives (the main competitor of IDE). But for compatibility reasons, all PCs will surely continue to support CHS addressing for many more years...

I have some more comments on TCJ #76: In his column, Herb Johnson partly confused the history of the GIDE development. My first IDE interface was a board for the ECB bus, accompanying the CPU280. This board was described in TCJ #56, more than three years ago. My circuit was used by Wayne Sung as a base for his development, a smaller interface for the Epson QX-10, which used an EPROM state machine instead of my GAL approach. About the same time, Claude Palm seemingly started developing the single-chip IDE controller PLD for use

in his Z180 SBC. However, I don't know if he was also inspired by my article in TCJ, or if we just had the same idea at the same time. In further discussion of his PLD chip, Herb Johnson, Bill Kibler, and I came to the conclusion that there was a need for a small and cheap interface which would connect to as many different computers as possible, so that was the start of the GIDE development.

The story of Claude Palm fighting his spurious FDC error is very interesting. Because of troubles like this, I always decode /IORQ with one of /RD or /WR to get valid select signals. This way, /M1 is not needed for the decoder at all. A very good design rule to prevent such problems is: Always use signals which are \*active\* to generate select signals, and never use \*inactive\* signals for this! In this case, never use "/M1 inactive" as a qualifier for I/O selection, but use "/RD or /WR active" for this purpose. This is a general rule which is a great help in many cases.

When Claude writes about his "18 MHz Z180", I assume this is not the real working frequency of the Z180. More probably, it is the frequency of the crystal which is devided by two to form the CPU clock. To my knowledge, the fastest Z180 chip available is the 12.5 MHz version. We should always use the real CPU clock, not the crystal frequency, when talking about clock frequencies anyway.

Regarding Bill Kibler's comments on CD-ROM access for CP/M: We are currently checking the possibilities for connecting a CD-ROM drive to GIDE. In my opinion, the best method will be a file transfer shell which allows you to navigate through the hierarchical file system of the CD-ROM and transfer selected files to the CP/M host. I don't think it makes much sense trying to establish a CD-ROM as virtual CP/M drive - the driver would be too complex, and would need additional hooks for accessing the different directory levels of the CD-ROM. That transfer shell could be about the same style as my "MSDOS Disk Emulator" for CP/M-Plus, which performs the same task for MS-DOS diskettes on any CP/M-Plus computer. However, those Linux CD-ROM driver sources surely are a good source of informa-

Wow, this is a rather long letter - more like a mini article. BTW,

hopefully I will find the time to explain and describe GIDE in detail in a future issue of TCJ.

Greetings, Tilmann Reh

Ed: The Zilog databooks list the Z8S180 as operating to 20MHz. See also Jonathan Taylor's message about GIDE and CD-ROM.

From: wayne sung

<wsung@jessica.Stanford.EDU>

. . . . . . . . . . . . . . . .

Subject: Re: Z80 SIO

It's been a while back, at a different job, that I did the SIO circuit, so this is from memory. What I was doing was trying to generate a stream of pulses to run a number of time clocks. These used a data format completely unlike rs232. I had a single board computer with a Z80 and SIO, so I took the incoming data from a radio clock into one of the SIO ports, changed the format, and was going to use the other port to generate the pulse stream to the clocks.

The clocks needed something like a pulse-width modulated signal at about a 2 kHz bit rate. This was where I found that using break didn't work. The clocks would never see the data. Using a scope I saw that the pulse widths were completely unpredictable. Changing to a control lead solved the problem. I seem to remember a statement in the data sheets that said something like break can be toggled at any time. Apparently it was not meant to say break will actually show up when I asked it to.

One interesting part of this project was that there is no ram at all. Since I didn't do any subroutine calls, and I didn't need many variables, everything was done in the registers (don't remember if I used the alternate set or not) and a 2 kbyte rom.

Another interesting part had to do with two different sources of timing information. Originally the clocks were driven from a generator which was "synced" to WWV. The reason the quotes are there is that it took a human to do the sync, i.e. someone listened to the WWV radio and pushed a set button to lock the clock.

After we obtained a WWVB clock to do NTP with, someone asked me if I could use it to run the building clocks as well. Being the gadget freak

I am, of course I tried it. Now the original generator put out a continuous signal, even though the digits were latched. So I decided I would put out only two updates a second (the time is..., I repeat the time is...)

Somewhere in the building there is a bit of crosstalk between the clock drive line and an intercom system. So by listening to the intercom one can tell which generator was driving the clocks. The original generator had a continuous 2 kHz tone, mine had two clicks close together every second. So I told them one was an analog clock and one was a digital clock.

Ah, the IDE project. Please forgive the long-winded introduction here, but the whole thing hinged on TCJ so hopefully you'll not be too bored.

I first "met" John Baker on the net. Still have never spoken to him personally, though there has been much email. What happened was somehow we got talking about something (don't even remember what now) and wound up fixing his Epson QX-10 completely via email.

I would ask him to try this or that, send measurements etc (boy it's hard to simulate a scope on email). Eventually we zeroed in and by faking one pin the machine came up. Turns out the caps in the power supply had dried out causing a lot of ripple on the 5v line so the power supply was keeping reset active.

John wrote a letter to TCJ about himself and included this particular episode as part of it.

At the same time, Tilmann Reh had also written up his IDE design in TCJ. It turns out one Mr Roche in France wanted some kind of HD adapter for his QX-10, and approached Reh about converting his design. Reh said he did not have a QX-10, hence couldn't do it, but that John Baker had one and to check there.

Of course John sends the request to me. I had a large bag full of registered high-speed eproms that were pulled from some comm equipment. I wanted to try using these for lookup table logic design, and this proved to be a workable project.

I was using mostly Reh's writeup for IDE description, but there was no feel for whether one polarity or the other of several pulses that might

work better. Rather than put in extra inverters, I put all the sequencing stuff (except one flip-flop) in the eprom. It also decoded whichever range of bus addresses I wanted.

This way I could just change the eprom bits to change polarities. Indeed two pulses wanted to be opposite what I assumed.

The final design had one LS08, one LS107, two LS646 and the eprom. Of course a pal design is just as possible, but I personally have had bad results with them. I think some other people I have corresponded with might have made pal designs.

One of the few times I beat Murphy to the finish line, but just barely. My QX-10 was already limping, having lost one floppy drive. Almost the very moment I got the first bios that really worked the second floppy died also, and I couldn't even reboot. I wrote up what I did, and John polished the bios. What I had done was change the sizes of the drives from 2 x 5 MB, which is what the bios had, to 2 X 8 MB. I did not think to expand the allocation vector, and eventually there would have been some funnies. John caught this and finished the changes.

Roche did not have email, a lot of this was done USPS, so it took maybe a year end-to-end. In the meantime I changed coasts and now don't even have any space to do 8-bit stuff any more.

John's link has been producing a steady stream of interest. The funniest request I got was from someone who wanted directions to build an IDE for a pc.

. . . . . . . . . . . . . . . .

Ed: I received this next message from John very early one Saturday morning.

From: "John D. Baker" <jdb8042@blkbox.COM> Subject: GIDE BIOS!

Just ten minutes or so ago, I brought up the first iteration of a CP/M 2.2 BIOS extension to support the GIDE on my Davidge DSB 4000 single-board computer!

I've just barely started testing. I'm going to bring up ZCPR-D&J as a minimum and then move to NZCOM to make the testing process nicer. Naturally, my BIOS extension

includes a ZDDOS clock driver...

The Davidge CP/M system has to be relocated for a 62K system and the GIDE extension is loaded at the top of memory and patched into the standard floppy-disk BIOS (DSB 4000 v1.3). I'm able to save quite a bit of space by using the data areas of the floppy-disk BIOS and only have to duplicate the disk-handling code (but it's greatly simplified).

As I've implemented it now, the floppy disks remain A: through D: and the hard disk is E: through I:. Naturally, I have to boot from the floppy disk at cold-start.

More as things develop, or as I develop things.

From: johntayl@spuddy.mew.co.uk (Johnathan Taylor)

Subject: Re: CP/M with alternate

BDOS support

(This message is in response to a message posted by Herb Johnson about the GIDE.)

Here's confirmation that Tilmanns G-IDE interface that Herb' speaks of not only handles big AT-IDE hard-drives flawlessly but it also works fine on ATAPI-IDE CD-ROM drives at the same time! I'm currently working on porting a POSIX CD-ROM reader util to z80-CP/M so that G-IDE users can access the CP/M and C-UG CD-ROMs directly! NO bios support will be required as it'll contain it's own driver. I've yet to decide how to implement the user definable I/O location, there's three choices:-

1/ End user edits sources and recompiles.

2/ Incorporate a patch table ie a cut down ZMP15 style jobby 3/ use the Hi-Tech C 3.09

"ENVIRON" file to store the custom settings in plain text form for the really non-technical!

I think 3 would be the most user friendly but 2 would be the most rugged across search search paths, etc., and 1 means that the end user must have Hi-Tech C and enough TPA/

floppy storage to perform the compile. For now all I need is a UK source for the CP/M CD-ROM itself as the CD-ROM's I've got were donated, bought-in-error, games-console CD's so don't have much of an iso-filesytem to test the utility ie. they only have 4 files and it's easier just to read the dirblock and manually load the 4 files!

Regards, Johnathan.

Ed: I received this note from Johnathan also.

I have obtained a copy of the CP/M CD-ROM and have manually retrieved a couple of files using raw block reads to decipher the CD-ROM directory structures and simply spooling consecutive blocks to a file to retrieve the actual file. Next comes the task of teaching the computer to search the CD-ROM itself.

And GIDE on the TRS-80.

From: Pete Cervasio <a href="mailto:cervasio@airmail.net">cervasio@airmail.net</a>>

Subject: Got the GIDE (mostly) working

Hi, Dave.

As the subject says, I managed to get the TRSDOS hard disk driver modified to work with the GIDE. It needs a lot of work before I would call it finished, but I've got data on a 340 meg drive as I type. I haven't fixed it to allow a logical drive to start at any physical cylinder, and there's still the limit of 202 tracks (with 2 physical = 1 logical), 8 heads and 32 sectors per track. The cylinder offset will fix the track limit, while the others will take fundamental changes to the way the drive control table is defined. I think there are enough bits that aren't used with hard drives that I can fix it.

I just started to write a bunch of stuff about the inner workings of TRSDOS, explaining what I'm running into. It'll be better in the article, which I've started on. How many words should I shoot for as a maximum before I split it into two or more parts? If you want to print all the code.. the driver winds up at 30 pages, and the "formatter" is about the same. Most of the driver listing is asking the user questions, and the same is true of the formatter. I could chop those parts

out for the article and just say what they need to accomplish.

How about a couple of photos of the completed machine, with the extra power supply and the GIDE and IDE drive installed? I had to apply a hacksaw to the RF shielding to make it fit over the GIDE. There's not a lot of clearance there. I had an old 63 watt IBM-PC power supply that I liberated from it's case (the circuit board, I mean). That's mounted in the bottom of the computer and powers the hard disk and the two floppy drives. The supply that powers the rest of the machine seems happier now that the floppies have "disappeared". :-) The PC supply just squeaks in under the monitor, with maybe 1/2" clearance between a big resistor and the tube. The hard drive (and a 3.5" 720k floppy) are taking the place of one of the 5.25 floppy drives. Personally, I think it looks great.

Well, I better get to bed. It's way too late and I'm getting "punchy". I just had to tell someone about this first. :-)

. . . . . . . . . . . . . . . . . . .

Talk to you later., Pete C.

From: Steven Young <syoung@nucleus.com>

To: tcj@psyber.com

Subject: Greetings!

# Greetings!

A few CP/M users and I have recently founded a fledgling organization - the CP/M Programmer's Organization, or CPO. The goal of this organization is to breathe some fresh life into the CP/M scene. After all, most software is at the least six years old, and has, on the whole, become just a wee bit stagnant.

The two major goals of the CPO are to:

- 1) Bring current public domain software up to speed with current developments. Obviously, nothing too flashy, since CP/M does only allow sixty-four K ram, but, for example, grafting OOP onto a C compiler, or even creating a C++ compiler, might be nice.

- 2) To create new software to fill the void of new software which has occcurred. For example, porting vi to CP/M is one of the projects we're look-

ing into.

Mind you, it's still, as I say, fledgling, and as of yet, we're still in the process of getting organized. But nevertheless, initial interest has been amazing, and I seriously think the CPO will prove to be, at the very least, an educational exercise. (and a bit of nostalgia for the greybeards, of course.;))

Ed: I don't know who he could be talking about. We haven't published any photos of any greybeards.

From: Ron Anderson <RWilAnders@aol.com> To: tcj@psyber.com Subject: Antique Laptop

Someone gave me a non-working Toshiba Laptop model T1200. I have it working but I would be happy to find any documentation for it. It has a 10 Mhz 8086, one floppy drive 3.5" 720K, an LCD screen, a NiCad battery pack and a charger/power supply. Having the 8086 ought to qualify it for antique status. I'm thinking of offering \$20 for it. I can use some of my "antique" software and use it as a word processor. I have used that same antique editor to write columns. If nobody there knows anything about it maybe you could put in a "letter" asking for help.

Thanks, Ron Anderson

Ed: Here you are, Ron.

From: Stephen Stone <stephen@silcom.com> Subject: Re: WTB: CP/M Formfilling Software

I was one of the original members of the KayPro Users Group of Santa Barbara in 1983. In 1987, our membership combined with that of the Osborne Santa Barbara Users Group and became the Santa Barbara Classic Computer Society. Our meetings still take place in the Goleta Library at 7 p.m. on the second Tuesday of each month. Attendance ranges from 8 to 14 persons. We had an anniversary celebration in 1993 with 25 people attending. Most discussion in meetings is mix of 8 bit nostalgia and discussion of what we consider to be ideal use of computer technology and technology in general. We actively help newcomers and oldtimers seeking information and help with older computers. We charge dues only when we find our treasury running low. Our monthly newletter survives because CP/ M programming genius Al Paarman continues to write interesting and irreverent articles for it.

My garage has more than 10 and less than 20 old 8 bit machines stored in nooks and crannies at any time. One of our members must have close to 200 old computers!

I still use my KayPros for word processing and keep my small business accounting with Checks And Balances. In the last year, I introduced one of our department managers in my hospital to one of my KayPros because our non-profit budget will not allow the purchase of computers for our department and her correspondence load was overwhelming our unit secretrary. The manager endured all kinds of gaff from visitors to the department for having this strange box on her desk she actually put the machine away because she was embarrassed to be seen with it! Then the burden of increasing work convinced her to try WordStar on the KayPro again. Now she loves it and won't part with the loaned 4-84 . . . . one less machine in my garage, I guess.

I've never gotten into ZCPR — but have used all of Plu\*Perfect Systems' enhancements. While I am not a computer professional, my background in CP/M machines has taught me to think about computers in an meaningful and evolutionary way: seeing computer science as more representative of what people can do with extensions of their knowledge about the need to work and communicate, than as a means to create appliances to be bought for the short-lived thrill of gee wiz features.

My latest desire for some of my 8 bit machines is to have them help me and my friends at work complete the mass of charting on preprinted forms which is now required in any health care setting. If I can find the form filling software for the KayPro which will allow us to type rather than handwrite our medical record entries, it will allow so much more time for care to patients.

Please read Stephen's ad in the Classified's too.

# Real Computing

By Rick Rodman

32-Bit Systems

All Readers

Free BSD, NextStep

#### FreeBSD 2.0

It took some doing, but I managed to collect together enough components from various computers to build one that will run FreeBSD 2.0. FreeBSD only supports a couple of SCSI host adapters - Adaptec and Buslogic.

As with most experimental operating systems, the installation process is nightmarish. Nothing is automated at all. There is a Readme file which explains the mysterious "Disklabel" procedure - but you can only see it from MS-DOS. Once you begin the installation, you can only see a very limited "tutorial" - which is a cruel misnomer, since it gives neither step-by-step instructions nor examples.

Why is it so hard to write installation programs? There are two well-known, commonly accepted principles: First, show all choices to the user at each decision point, with automatic defaults which clearly show the most likely user choice. Second, the user should make all the decisions up front. The user should not have to make a choice, wait five minutes, make another choice, wait five minutes, and so on. The FreeBSD installation procedure flunks both of these principles. Is this because Unix gurus are elitist snobs who feel that neophytes must be forced to struggle? Or because their brains are so warped by repeated mystic incantations that they truly believe that small letters and uppercase letters are totally different and unrelated? Or are they unable to write an installation procedure because their computers already have umpteen copies of FreeBSD already on them? I think it's the latter. Actually, the FreeBSD folks really did try - they made an install script that automates some of the work - but they have a much longer way to go.

The installation has four parts: Fdisk, Disklabel, rebooting, and installing "distributions".

The Fdisk program is pretty standard, with one little gotcha. There is a command for writing a boot record and another for writing an "MBR". To me, MBR stands for Master Boot Record and so these ought to be the same, but they aren't. The MBR refers to a multiple-operating-system boot routine which doesn't appear to work, so just use the regular "w".

Here's the story behind the Disklabel part: FreeBSD calls disk partitions "slices" and subdivides these with a program called "disklabel". There are eight subdivisions which are named "a" through "h", but on a fresh disk they initially contain garbage. You need to delete "e" through "h" first, then do a (W)rite. Next, you need to (E)dit "a" for about 18 megabytes, "b" for about 16 megabytes, and "e" for what's left. You can't change "c" or "d". Do another (W)rite. Next, you need to (A)ssign "a" to mountpoint "/ ". (A)ssign "b" but you don't enter a mountpoint, and (A)ssign "c" for "/ usr". Then do a (W)rite and a (Q)uit.

When you say (P)roceed, the machine has to reboot. This is a surprisingly iffy step. Actually, most of the 32-bit OSs have a reboot halfway through, including OS/2 and NT, and it's a sort of checkpoint as to whether things are going to continue to work.

Installing the distributions is a very long process, requiring you to make a decision, wait anywhere from a few minutes to half an hour or more, make another decision, wait another long time, and so on.

The installation crashed on me while installing Xfree86. Once this happened, I couldn't find any way to resume it. I didn't want to start completely over because I'd already spent over 4 hours on the process. I logged in as root and poked around. The mystic incantation to mount the CD-ROM is:

mount -t cd9660 /dev/cd0a /mnt

Which is similar, but of course completely different in all the details, to mount commands used under Linux or SunOS. This is one of the pitfalls of Unix: Because so much is installation-dependent, you can be a Unix expert and yet not be able to find or do anything in a different version.

The file INSTALL, which can be read from the CD, mentions briefly that the installation can be resumed with /sbin/ sysinstall, or that a "package" (same as a distribution?) can be added with pkg\_add (which turns out to be in / usr/sbin). Both of these statements appear to be wrong; there's no apparent way to resume an installation. So, I couldn't test X Window. The text-mode OS works fine, but I didn't see anything new or different. In fact, much of what you get with FreeBSD is exactly identical to what you get with Linux, with the same source code.

In summary, FreeBSD has little to recommend it over Linux. Linux costs less, includes more, and is much easier to install. I hate to denigrate somebody's labor of love, but it needs less love and more labor.

# NextStep

NextStep is another 32-bit OS which doesn't include source code. Since I went through the hassle of attempting

to install, I thought I'd warn the unwary who might be suckered in by the OOH (Object-Oriented Hype). The first thing to know is that NextStep supports only two SCSI host adapters: the Adaptec 154x, and a DPT EISA caching host adapter. You must have one or the other. And get this: You're only allowed to have a single 1.44 megabyte floppy attached. You're not permitted to have a second floppy!

I was going to install version 3.2, but its installation procedure crashed every time at the point of trying to talk to the Adaptec board. Version 3.1 hung every time, usually at the beginning, sometimes a little further on. The manual says: "You may need to rerun the installation several times before it works." Can you believe that they print such an admission of incompetence right in the manual?

Instead of requiring you to do a mysterious Disklabel, NextStep always asks you questions along the line of "Do you want to install NextStep? Press 1 for yes, 2 for no." You get asked this question several times. The manuals, even the installation manuals, while full of beautiful screen shots, are almost devoid of any technical information. Next has a fax-back system for anyone who needs to know anything technical. They have an email system too, but you have to have NextStep installed to use it. Like most software companies these days, they picture information exchange as only flowing in the outward direction.

I never did get NextStep to work. Evidently its marketplace obscurity is well-deserved.

After this installment, I'm not going to review any more operating systems, for a while at least. I recommend only three operating systems for PCs: Linux (Slackware or Yggdrasil), Windows NT, and OS/2 Warp. I'll probably recommend Minix 1.7 when the release comes out.

# Peer-to-peer networking under DOS

In version 6 of MS-DOS, Microsoft quietly slipped in a two-station LAN. It consists of two EXE files, which are also device drivers, INTERLNK.EXE and INTERSVR.EXE. Connections

can be made via serial or parallel ports. You put DEVICE=INTERLNK.EXE in the CONFIG.SYS files of both machines, then run the command INTERSVR on the server and INTERLNK E:=C: (for example) on the client. Presto, the client can access the server's drive.

This got me to thinking about the small-machine network. File transfer is not really very convenient. Yet drive mapping is complicated and very OSspecific, involving interception of filelevel OS calls. But what if we trapped BIOS calls instead? There's only a couple of calls that would need to be intercepted, and performance would actually not be much worse. The problems would be related to file sharing, directory entries, and block allocation (allocation vector bits). Yet, in the CP/M case at least, these involve data which is accessible to the BIOS. Furthermore, in a small-machine network, we can restrict who has write access, giving all but one user read-only access if desired.

I was thinking about this in the context of the wonderful CP/M CD-ROM from Walnut Creek. Right now, getting files from it to a CP/M system is cumbersome. There ought to be a way that I could map a group of files, let's say a subdirectory, to a virtual CP/M drive (which is limited to only 8 megabytes), and access it through a serial port as though it were a hard drive.

A small LAN or OS simply can't afford the space to do it the way the big guys do. We've got to cut corners and get away from the layers which, while making big systems more reliable, reduce efficiency and increase code size.

# The Intronics Pocket Programmer

Just a brief mention of this product, which works really well. This is an EPROM programmer which attaches to a PC's parallel port - no board required - and costs only \$130. It has a ribbon cable and a YAWT (Yet Another Wall Transformer), and a diskette containing the software. It'll program any single-supply EPROM; you can get adapters for MCUs, too, but they cost almost as much as the programmer itself. Anyway, this is a great product. I was afraid it'd be slow, going through the parallel port,

but it's just as fast as my old programmer, and a lot more convenient. Now I can easily take the programmer and my laptop to the equipment and copy or reburn PROMs right there. If you're in the market for a PROM programmer, think hard about it.

#### Next time

Next time we'll move from the Mall to the small. I'll show you how to use Small-C to generate a firmware program to run from PROM. Plus, we'll have some words about the joys of computer telephony.

# For more information

Real Computing BBS/Fax: +1-703-759-1169 E-mail: ricker@erols.com Mail: 1150 Kettle Pond Lane Great Falls, VA 22066-1614

Walnut Creek CD-ROM (Manufacturer - FreeBSD 2.0 and CP/M CD-ROM) 1547 Palos Verdes Mall Suite 260, Walnut Creek CA 94596 +1 510 676 0783

Next Computer, Inc. (Manufacturer - NextStep) 900 Chesapeake Drive, Redwood City CA 94063

Intronics, Inc. (Manufacturer - Pocket Programmer) P.O. Box 13723 Edwardsville KS 66113 +1 913 422 2094

# LINUX

| InfoMagic 5 CD Set            | \$21.95 |

|-------------------------------|---------|

| Yggdrasil                     | \$29.95 |

| Linux man Pages               | \$29.95 |

| The New Book of Linux \$29.95 |         |

| Call for other titles         |         |

www.justcomp.com

on the World Wide Web

# JUST COMPUTERS! (800) 800-1648

Fax (707) 586-5606 Int'l (707) 586-5600

P.O. Box 751414, Petaluma, CA 94975-1414

E-mail: sales@justcomp.com

Visa/MC/Int'l Orders Gladly Accepted

For catalog, send e-mail: info@justcomp.com

Include "help" on a single line in the message.

# Mr. Kaypro

By Charles B. Stafford

Regular Feature

Kaypro Support

Composite Video

#### **BARRY COLE ROMs**

Since we last conversed, in issue 74, (mea cullpa, mea culpa) there has been a great deal of excitement. I actually got to meet and talk with Barry Cole. For those of you to whom this doesn't mean anything, don't feel bad! Up until about a year ago I didn't know anything about Barry either.

Back in 1983, the dark ages, when the '84 series Kaypros were but a gleam in Andy Kay's eye. Barry was repairing about 20 K-IIs and K-4s a week and modifying quite a few of them. When the '84s came out he decided that since they had a larger monitor rom and the appropriate signals were close by, that booting from disk was for the birds and other computers. Reality was just a few short days (weeks) away with the birth of the Barry Cole Rom. He used a 27128 (16k), twice the size of the stock 2764 (8k), 4 times the size of the K-4s 2732 and 8 times the size of the 2716 in the original design (Kaycomps and K-IIs). The code included not only the bios (basic input/output system) and bdos (basic disk operating system) but also a CCP (console command processor) based on ZCPR 2. This meant that he was completely free of Digital Research's copyrights and patents, and the term "boot disk" became meaningless. In fact, according to Barry's promotional literature, a machine with his rom will boot with a piece of cardboard in the drive.

Barry has included a version of ZCPR, as well as bdos changes that will accommodate two 10 meg hard drives or one 20 meg hard drive. You'll still need to make the hardware changes, of course, but the support is there. The command set understood by the CCP

has not only the original 6 embedded ones, (DIR, ERA, SAVE, USER, TYPE & REN) but also:

LIST (sends the file to the printer)

GO (re-executes a previously loaded program)

GET (loads a program at a specified address)

JUMP (executes a program at a specified address other than 0100h)

SAFE (parks a hard drive if installed)

DISK (a built-in copy, era etc utility)

D (a super directory clone)

BOOT (boots from a floppy in

drive A)

NORM (initiates "protected" mode disabling most commands, for bbs or similar use) and

PASS (+ a password, undoes the effect of NORM).

The modifications also specifically report disk malfunctions and eliminate most resets (such as aborting a faulty disk write).

The bad news is that I haven't got the ROMs yet. The good news is that I expect to get them in the 1st quarter of 1996. Watch this space for notification.

#### ON TO MORE TANGIBLE STUFF

Herewith, the promised follow-up to the external composite video project we did in TCJ #74.

Our objective is to understand the project sufficiently to be able to modify it to fit all CP/M Kaypros, and use

both composite and TTL monitors (DB-9 connections).

#### THEORY

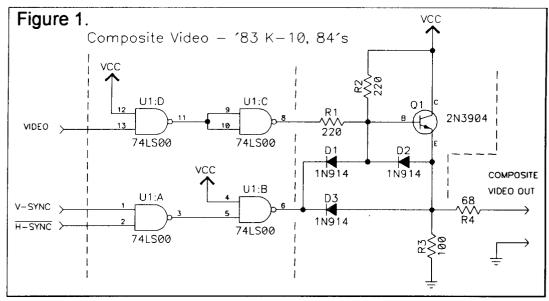

The circuit actually consists of five stages; the input signals, the buffers, the mixer, a driver and the output signal(s). See figure 1.

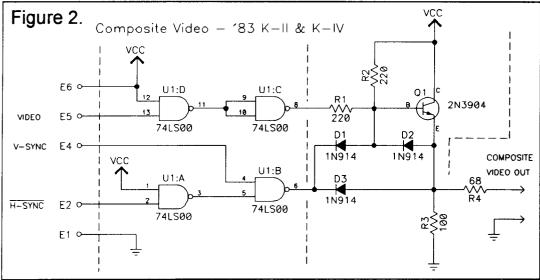

In the last project we took the input signals as well as ground and 5V from the pins of U1, a 7406 that we removed and out in a wirewrap socket. This works very well for the '83 K-10s and all the '84 models, but not so well for the '83 K-IIs and K-IVs. These machines, however, have a row of test points, labeled E1-E6, just toward the front of the computer from the Centronics connector for the parallel port. They have all the signals we need with the exception that the vertical sync is inverted. If the solder in these test points were removed, (easily done with a small soldering iron and a "solder sucker" or wick), we could mount a six pin header, and use it to plug on a "daughter" board. To take care of the vertical sync the connections to pins 1 and 4 must be switched with the vertical sync signal from E4 going to pin 4 and pin 1 being tied "high". See Figure 2.

Since the '83 K-IIs & K-IVs use the same vertical and horizontal sync frequencies as standard composite (& close to TTL Monochrome, by the way) monitors, no tweaking or "monkeying around" is needed. We can now use this circuit in any CP/M Kaypro.

Our next trick is to adapt this circuit to TTL monitors using a DB-9 output connector so we can use "standard" external monitors. The advantage of this is that an EGA monitor will "sync"

9

right up to an '84 K-anything or an '83 K-10 without any tweaking, and a CGA monitor will "sync" right up to an '83 K-II or K-IV without tweaking. A monochrome monitor, though, may need a "Sync" adjustment, but the stock K-II or K-IV frequency should be within the monitor's range.

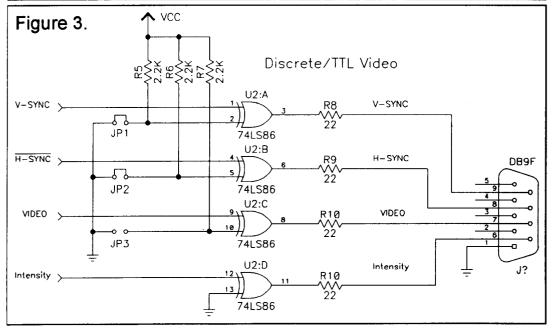

The 741s00 that was used in the last circuit, has 4 inverting "nand" gates. Buffering a signal, and getting it right side up, requires the use of two gates. Since there are three signals involved (Horizontal sync, Vertical sync and video) six gates would be necessary, two more than are available. If, however, a 741s86 is used, our problem is solved. A 741s86 is a four section exclusive "or" gate, which, with one input tied "low" (to ground), becomes a non-inverting buffer. This means that signals can be picked up from either the 7406 (in the case of an '84 machine or an '83 K-10) or E1-E6 (in the case of the "83 K-IIs or K-IVs), run through one section each of the 74ls86 and then to the appropriate pin of a female DB-9 connector. Use of a jumper on the vertical buffer to select inverting or non-inverting provides for those monitors that expect inverted vertical sync. See Figure 3.

Which signal goes on which pin depends on the monitor the circuit is intended for.

| <u>Pin</u> | Mono   | CGA    | EGA   |

|------------|--------|--------|-------|

| 1          | gnd    | gnd    | gnd   |

| 2          | gnd    | gnd    | open  |

| 3          | •      | open   | open  |

| 4          | -      | open   | open  |

| 5          | -      | open   | open  |

| 6          | open   | video  | open  |

| 7          | video  | open   | video |

| 8          | Hsync  | Hsync  | Hsync |

| 9          | -Vsync | -Vsync | Vsync |

|            |        |        |       |

Mixing and Matching choices of the input signal methods, buffering methods and output signal schema will result in an easily constructed circuit customized just for your machine, and will probably be the only one like in existance for miles around.

# EXECUTION (or CONSTRUCTION, if you prefer)

After you have made the appropriate choices, and drawn or copied the a

schematic diagram, a parts list can be compiled. Almost all the resulting parts lists will include a couple of 100 ohm resistors, an IC (741s00 or 741s86), at least one socket perhaps two, an output connector, some ribbon cable or coax, a six pin header and female connector or wire wrap socket, and a prototype printed circuit board to build it on. The same sort of prototype board that was used in the first project will work here as well.

Connector mounting can be a challenge. On the first project, a panel mount RCA socket was used. It was the type that is supposed to go into a hole from the front of the panel and have a nut put on from the rear. Flats were filed on two sides of the connector, so that it just fit in one of the ventilation slots on the back of the case. The slot could have been enlarged, but that would have involved cutting on the case and this solution seemed cleaner. Mounting a DB-9 female connector is a little more involved. If a slot is filed just a little wider, the DB-9 will fit just fine. A hole can be drilled just below the slot to accomodate one of the mounting screws, and a small piece of scrap metal can be fashioned and drilled to accomodate the other. A simpler solution is to find a standard "IBM" type slot cover which has been punched for a DB-9 connector, cut the ends off 3/ 8" outside the mounting holes, drill two more 3/16"holes (one at each end) and mount this adapter over a ventilation slot using screws and nuts with washers to bridge the slot on the inside.

# **CUTTING THE CASE**

If you decide to file, drill or cut the case, the safest way is to remove all the electronics, modify the case, clean it of all chips and filings and then reinstall the electronics.

There is, however, an easier alternative which, if done carefully, is equally as effective. Using Duct Tape (two inch or three inch width), fasten two or more strips edge to edge about six inches long with a 1/4" overlap at the edges, sticky side up, on the workbench. This should result in a single piece about six inches by four or six

inches. Stick one end on the inside of the case, parallel to the bottom of the case about an inch above the area to be cut, filed or drilled and the other end, also parallel to the bottom of the case about one inch below the area to be cut, filed or drilled. Now pinch the sides together, forming a tent over the work site, on the inside of the case. Cut, file or drill to your hearts content, and when you are satisfied with the result, smash the tent down on the inside of the case to pick up all the stray metal chips inside, and remove it carefully. Then inspect the area to insure that you didn't let any chips escape.

This procedure sounds complicated, and takes a lot longer to describe than do, but read it first and you'll see how simple it really is.

# **NEXT PROJECT**

An internal modem (you pick the speed) for ALL the CP/M Kaypros.

# A LITTLE COMMERCIAL

Recently I have been fortunate enough to find a limited supply of Kaypro monitors which include both the CRT and the Video board, as well as, mother boards (both '83 and '84 varieties) and a few WD1002-05 hard drive controllers. Monitors are \$50.00 but the mother boards vary depending upon condition.

# Advent Kaypro Upgrades

TurboROM. Allows flexible configuration of your entire system, read/ write additional formats and more, only \$35.

Replacement Floppy drives and Hard Drive Conversion Kits. Call or write for availability & pricing.

Call (916)483-0312

eves, weekends or write

Chuck Stafford

4000 Norris Ave.

Sacramento, CA 95821

# The European Beat

by Helmut Jungkunz

Regular Feature

All Users

East German Z80 + GIDE

# Finally - Hi-Tech for the looneys!

Well, well, if history doesn't go strange ways! I used to dream with my friends of the wonderful things happening in the US and we used to feel pretty lousy about our impossible situation: no RS232C on our computers (by default), very little or poor local programming, and very expensive hardware, by far higher priced than the equivalent in "Amerika".

Many of us were also suffering from being unable to understand enough English and none of the documentation and source code were available in German, French, Spanish at all

Then, after all these years, we see the American standards drop next to zero almost overnight! What a shock. Here is, where our typical European "being behind" finally works out: the continuing industrial use of Z80 based equipment has brought up some new products, like Tilmann Reh's CPU280.

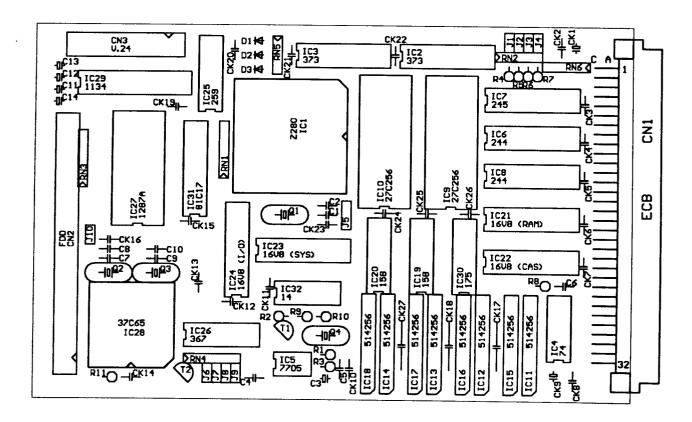

A small board that (besides it's outstanding, innovative design) is based on a very common industrial bus system, the "ECB-Bus". This allowed people to develop peripheral devices that would also be usable in other machines. This concept was probably the reason why Tilmann developed not only a nifty Hercules terminal and an IDE interface to make AT-BUS (IDE) hard disks available to CP/M users, but he also decided to take up the concept of a Generic IDE interface (GIDE) from an idea of a couple people. So Tilmann sat down and did the work!

# The results are overwhelming:

A small board plugs into the (Z80) CPU socket of any Z80 CP/M computer, where the Z80 itself is then sitting on top of the GIDE, in the extension socket present there. At the Trenton Computer Festival '95 I was able to make a (poor, but successful) demonstration of how to mount the GIDE in a KAYPRO 4/10, a computer I, so far, only knew from books. The failing point was a defective hard drive I had purchased at the Trenton flea market. Still, the ease of the procedure could be shown.

Despite the bad condition of the drive, I could make all connections and use the test program once(!). It showed the drive identification (an IDE standard) and did some efforts to read randomly selected sectors. Then the drive died.

I was very upset at that day, having traveled all the way from Germany only to be ripped by some cat in the fleamarket, since it was impossible for me to bring along an IDE drive, and neither I nor Jay were able to arrange for one for the demo.

I got back to Tilmann after my return and told him, that his interface was basically a great success. I got people from our AMSTRAD user group (SCUG) interested and also the people from the JOYCE USER AG, a German PCW group. The thing is, besides the easy hardware side, implementing a hard drive into the BIOS is a different story. We still don't have an implementation for the CPC. What a shame! But, at the same time, I want to report that the implementation by the JOYCE USER AG people was already successful.

I planned to show the PCW GIDE at our club's 10th anniversary. Unfortunately, the drive kit arrived late. The only good thing was, that a few days afterwards, our regular club meeting took place. I then arranged to have the important people there and I brought my PCW along.

After a test run of the PCW showed that it was working, we went to disassemble the machine. It turned out, that some of the screws were much longer than expected. Then we carefully marked all the wires and took off the sheet metal screen that is used as a high-frequency shielding. Then we slid out the Main board (right next to the drive(s)) and removed the Z80 CPU. The kit we had received from Reiner Seitz contained all of the cables and connectors necessary. The only thing one has to supply is the power. No problem, if you only have one drive, simply use the second drives power supply.

But be warned !!!!! The PCW drive supply connector looks identical to the standard 3.5 inch connectors - but are reversed between 5 and 12 Volts!!!!

Anyway, once the Z80 was plugged into the GIDE, we immediately fired up the PCW (still without the hard disk connected), to see if it was all working. It came up fault-lessly, so we became more audacious and hooked up the IDE drive. Then we used the special startup disk supplied by Reiner Seitz. It uses a more up-to-date BIOS version (1.8) that allows the use of special loader files, a similar technique like the IMP overlays or such. The big advantage with the PCW's CP/M Plus here is that the banked system can be hidden and overlaid if enough memory is available. Thus, the PCW's TPA stays practically unaltered. This is fantastic, since all the programs run in no time at all and behave well. One has to know, there is lots of rubbish about that uses absolute addresses in the PCW system memory.

Naturally, we used the HDFORM tool from Reiner to see what it did. It performed a flashy clean-up of the hard disks directory to allow proper CP/M Plus data entry. Then I wanted to see more and copied an existing installation of Z3PLUS onto the hard disk. What shall I say, it ran "out of the box" in no time at all. The drive in the PCW is implemented in a superfast environment. It's performance may well be compared to 486 speed. Amazing!

I was so impressed, I was smashed to bits. (8)

Then, to top this, a week later, Joerg Linder calls me and tells me, the KC user group had decided to throw their "MicroDOS", a cheap and dirty CP/M clone with added features, overboard, in order to achieve true CP/M capabilities. We discussed different alternatives and I had sent him a copy of Hal Bower's CHEAPLAN TALK, that I had filmed on location at Trenton in April '95. So he agreed, that ZSDOS might be a good choice. I arranged for a package deal, and it seems, the KC85/4 (remember TCJ back issue #75) will be the first European Computer to use ZSDOS by standard! Imagine, over 50 people will be using ZSDOS! Then, I also recommended that they implement ZCPR34 and got another package agreement with Jay Sage for the lot.

They had been fiddling about with the garbled operating system of the KC85/4 in order to not only resource it, but to finally separate the mixed codes for BIOS, BDOS and part of the CCP, that by then couldn't be overwritten! When they were about to give up, Mario Leubner, the chief assembler programmer of the KC User Group, found a few clues that allowed him to rewrite large parts and rethread, what was going on.

So, to my amazement (again), I got a message from Joerg, announcing not only the successful implementation of ZSDOS, but also a new CCP that could be overwritten and - a fully implemented GIDE drive! They also rewrote the RAM access and the CPU sharing, which makes the new KC85/4 practically a new computer. I am pleased to report all these happy events, that took place in the same period

when Bill Gates tried to sell Windows 95 to the Germans. Do I have to say, his success was poor here?

With all these happy thoughts in mind, I want to wish you all a successful and happy 1996! (no, it is never too late, I just proved it above!)

Regards, Helmut Jungkunz ZNODE 51

P.S: I filmed the KC85/4 presentation at Z-Fest 95, some of our 10th SCUG anniversary and also the PCW GIDE test on Hi-8. I copied this to VHS NTSC and sent a copy to Don Maslin and Michael Crafton. I don't know if anyone of them can duplicate VHS cassettes in decent quality, but if so, they are welcome to do so.

# Special Feature Intermediate Users PLD Application

# Hands on with PLD's

by Robert Brown

#### INTRODUCTION

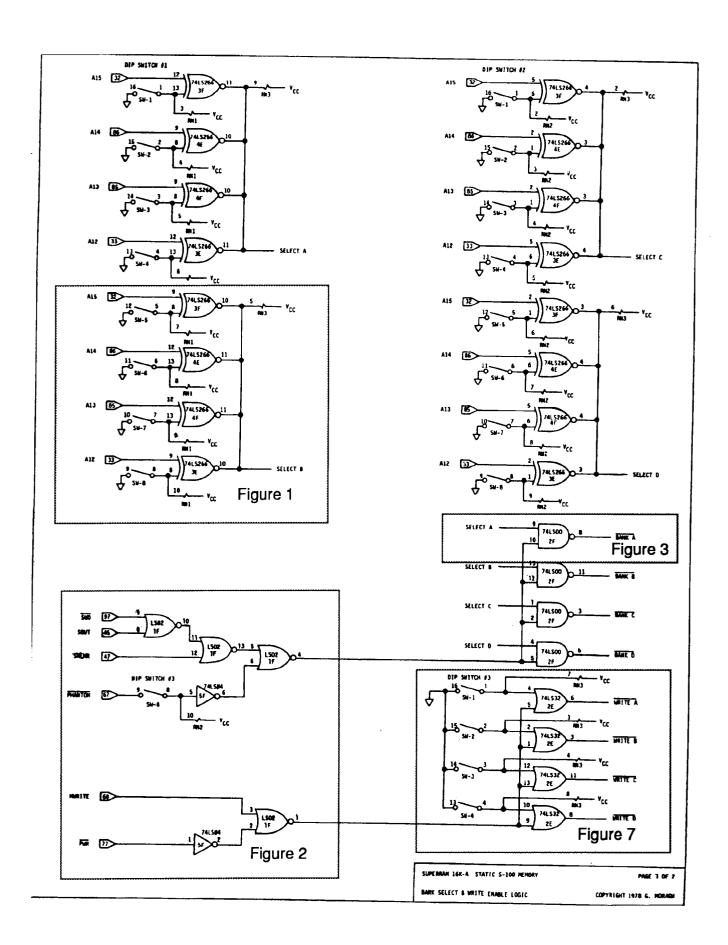

The introduction of programmable logic devices (PLDs) was a great boon to the field of digital hardware design. The second generation PLD, the GAL (which stands for Generic Array Logic, a trademark of Lattice Semiconductor) is particularly suited for the small scale hardware designer. GALs offer the following benefits to the hardware designer:

Flexibility - GALs are very flexible devices, they can implement both combinatorial logic functions (AND, OR, NAND etc.) and registered logic functions (counters, shift registers etc.) on the same chip.

PAL replacement- The GAL16V8 and GAL20V8 each can directly replace over 20 of the common PAL (Programmable Array Logic - the first generation PLD) types each. This means you only need to stock 2 GAL types to handle your PLD needs.

Space savings - In my experience each GAL has typically replaced between 2 and 4 standard TTL chips, saving a large amount of board space.

Speed - GALs are fast devices with propagation delay down as low as 7 ns. Typical GALs have a propagation delay of only 15 ns - faster than standard 7400 or 74LS series logic.

Reprogrammability - Not only are GALs programmable giving the ability to correct design errors and make board layout easier, they can be reprogrammed up to 100 times. Erasing and programming takes only a few seconds.

Cost - In addition to the savings in PC board real estate, standard speed GAL16V8s and GAL20V8s (25 and 15 ns) cost only a few dollars even in small quantities.

There are several varieties of GALs but I will limit this article to the GAL16V8 and GAL20V8. They are easy to design with and are the least expensive and most readily available GAL devices. Rather then get bogged down with the internal details of the devices, we'll cover what is needed to use these PLDs in your designs and then look at a real life design example.

#### The Device Architecture

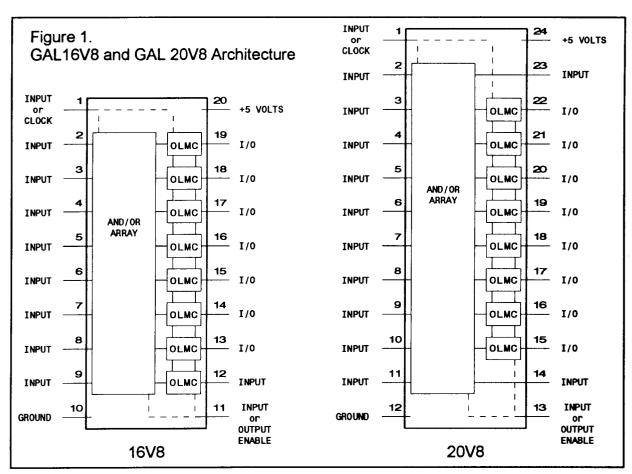

The GAL16V8 is commonly packaged in a standard 20 pin DIP and the GAL20V8 is commonly packaged in a 24 pin skinny DIP (a 24 pin skinny DIP is 0.3 inches wide, the same width as a 20 pin DIP and half the width of a standard 24 pin DIP). The pinout for both devices is shown in figure-1. For the GAL16V8 pin 10 is the ground pin and pin 20 the +5 volt pin (VCC). Pins 12 through 19 are each connected to Output Logic Macro Cells (OLMC). The OLMC allows these pins to act as inputs, combinatorial outputs, registered outputs and input/output pins. Pins 2 through 9 are always general purpose input pins. If any of the OLMC are configured as registered outputs then pin 1 is a Clock input and pin 11 is the Output Enable for the registered outputs. If none of the OLMC are registered then pins 1 and 11 are general purpose inputs. Internal to the chip is an array of and/or logic that is configured with each OLMC when the chip is programmed. The 20V8 has a similar design, the main difference from the 16V8 is the four additional input pins.

# The Design Tools

In addition to your PC you will need only three tools to do design work with PLDs, a text editor, a logic compiler and a device programmer. A logic compiler is a program that translates a high level design file, in which the relationship between inputs and outputs is expressed in the form of equations, to a low level file device specific file for the programmer. The low level file used by the programmer is called a JEDEC file and is sometimes referred to as a 'fuse map'. (Earlier PLDs were programmed by literally blowing up fuses internal to the device leaving only the desired connections - of course they could not be reprogrammed you threw away your mistakes.) National Semiconductor used to offer a FREE logic compiler before they got out of the PLD business. You can still get a copy of their PLAN or OPAL logic compilers off of many BBSes (including TCJ's). For the 16V8 and 20V8 you can use either PLAN or OPAL. The high level design file for PLAN is called an equation file and uses the extension .EQN, the output JEDEC file uses the extension '.JED'. Since PLAN is available to everyone I will use it in the examples, the concepts however are universal, not specific to PLAN. The equation file is a standard ASCII text file and can be produced using any text editor.

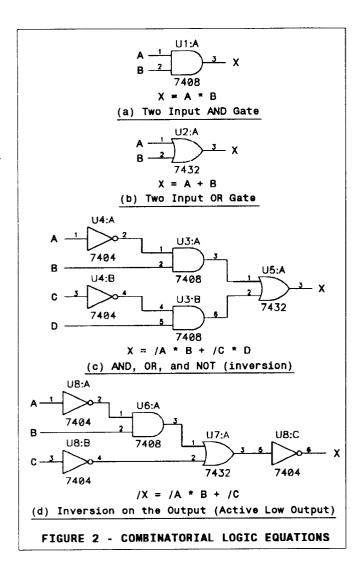

# Designing with Equations

If you normally design with standard TTL devices, shifting to design using GALs might take a slight adjustment. However the underlying concepts are the same. In the equations a + is used to represent OR, a \* to represent AND a / for NOT or inversion. In figure 2a show the equation represent by an AND gate. Each group of signals ANDed together is referred to as a product term. Figure 2b shows the equivalent representation for a two input OR gate. In figure 2c a more complicated piece of logic is represented, it includes the use of the / symbol to show inversion. Notice how the equation is organized. The equations are written in a sum of products format, a useful convention is to list each product term on a separate line. The inversion can also occur on the output as shown is in figure 2d. In the 16V8 and 20V8 up to eight outputs can be defined in this way (each of the eight OLMC). The inputs for the equations can come from any of the input or output pins either normal or inverted. A maximum of seven or eight product terms are allowed for each OLMC, this depends on the exact configuration of the OLMC. Given this, it is obvious that a single GAL can replace several packages of AND, NAND, NOR and OR gates. But this is only the start.

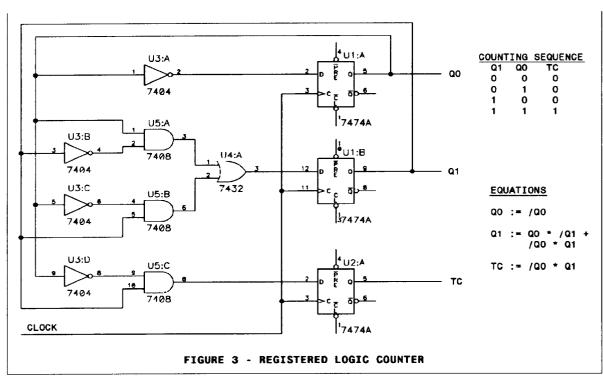

So far all the examples have used combinatorial logic, in addition GALs can also handle sequential logic such as shift registers and counters. To do this the OLMC is configured as a register (D flip flop). If any of OLMC are configured as registered then pin 1 is the clock input to the

register. Where as an = symbol is used to show a combinatorial output in an equation, a := symbol is used to show a registered equation output. For example:

The := indicates that the output Q is registered. This means that Q will take on the value of D following the rising edge of the clock on pin 1. Two or more outputs can be combined to form counters and shift registers as shown in figure 3. In this case it shows a two bit counter with a terminal count. The two outputs Q0 and Q1 will count from 0 to 3 continuously and the terminal count indication will be active when the count is at its maximum value of 3.

The registered outputs have a common output enable at pin 11 on a 16V8 and pin 13 on a 20V8. When output enable is low the registered outputs are all enabled. If output enable goes high all the registered outputs will be disabled (tri-stated). Even when the outputs are tri-stated the register outputs are still available internally as feedbacks (so the counter would continue to work even if the outputs were disabled). Combinatorial outputs can each have an output enable defined, this is limited to a single product term. For example:

X.OE = B \* C

This would indicate that output X should be enabled when B AND C are high.

# A Real Design Example

To illustrate the use of GALs in a real design, I will use the main board from a high speed, low cost 16 channel logic analyzer. The logic analyzer main board uses a total of 17 ICs, of these 2 are static RAMs, 4 are octal latches, 4 are octal buffers and the remaining 7 are programmed GAL16V8s. All standard logic was handled by the 7 Gals, they replace about 20 high speed TTL ICs and make the logic analyzer buildable. (For more information on the logic analyzer design download RGBLOGIC.ZIP from the TCJ BBS, the schematic and all of the EQN files are included in the file, so you can review the complete design.)

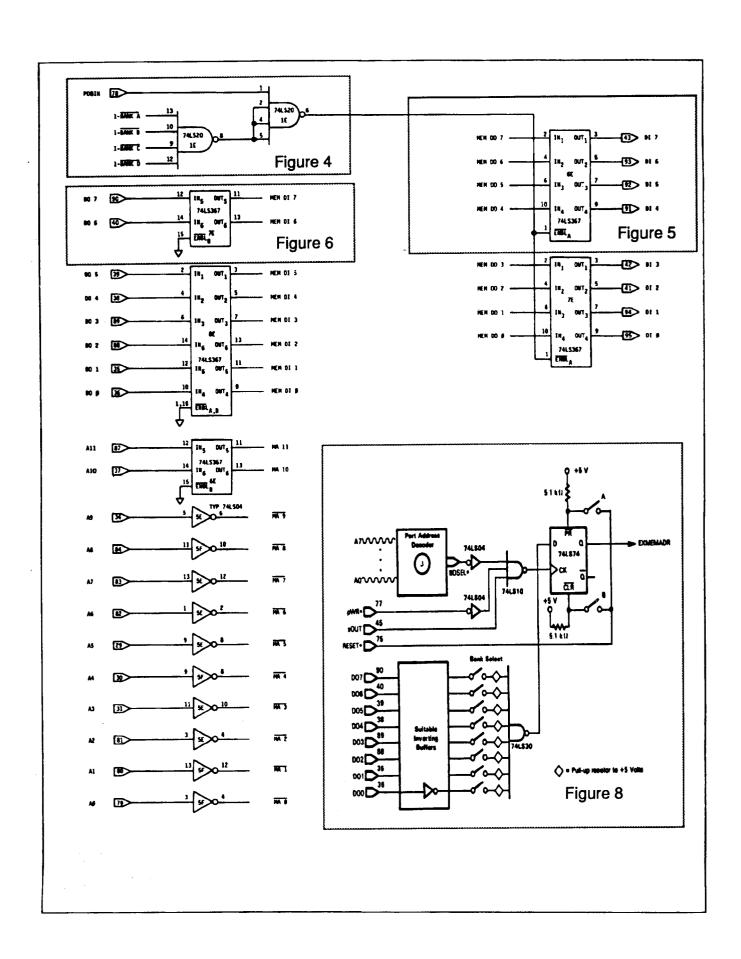

Central to the logic analyzer is the clock selection GAL. This allows the analyzer clock to be selected from 5 different internal clocks, an external clock or a software controlled clock. The PLAN equation file, CLOCK.EQN is shown in figure 4. The lines that start with a; are comment lines, they are ignored by the compiler and are used for documentation. The equation file must contain two sections, the declaration section and the equation section. The declaration section should appear first and is indicated by the keyword CHIP. The line:

CHIP clock 16V8

begins the declaration block, it gives the chip a name (clock) and selects the device type (16V8). The next part of the declaration block is optional, but will be needed in most cases. In this section we assign symbolic names to each pin on the chip, as follows:

clk nc ext self s2 s1 s0 dir wr gnd /oe sysclk1 wrdat sysclk0 q4 q3 q2 q1 q0 vcc

The symbolic names start with pin 1 and are assigned in order through pin 20. In this case pin 1 is assigned the name clk, pin 9 the name wr, pin 12 the name sysclk1 and pin 19 the name q0. If we later need to change the pin assignments, we simply rearranged the names given here.

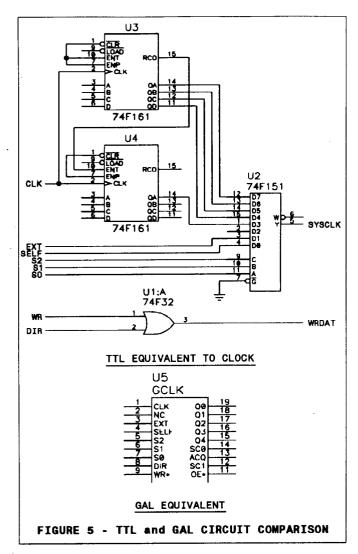

The equation section of the file is indicated by a line with the word EQUATIONS. Outputs q0, q1, q2, q3 and q4 form a 5 bit counter (a straight forward expansion of the 2 bit counter used before). This counter provides several reference frequencies at the outputs, q1 is half of q0, q2 is half of q1 etc. With a crystal oscillator of 40 Mhz connected to pin 1, q0 provides a 20 Mhz clock, q1 a 10 Mhz clock, q2 a 5 Mhz clock, q3 a 2.5 Mhz clock and q4 a 1.25 Mhz clock. The outputs sysclk0 and sysclk1 use identical equations, so I refer to them together as sysclk. The sysclk outputs are combinatorial, they allow the system clock to be selected from q0, q1, q2, q3, q4 or the inputs self or ext. The inputs s0, s1 and s2 select which clock is output to sysclk. From the equations you can see that if s0, s1 and s2 are all 0 then sysclk is the same as the input self. If s0, s1 and s2 are all 1 then the last product term will apply and sysclk will follow q0. The final output defined in the equations is wrdat, this is obviously just a simple two input OR function. I remember that Bill Kibler said he wanted to see the equivalent circuit in standard logic for all programmable logic used in TCJ. It is not always possible, but in this case I had first looked at designing the logic analyzer using standard logic. The equivalent circuit to this GAL is shown in the schematic in figure 5, notice the savings in chip count and cost.

The equation file is compiled with the command line:

EQN2JED -N CLOCK

EQN2JED is the PLAN program that produces the JEDEC file, this will take our CLOCK.EQN file check it for errors and if error free produce the JEDEC file CLOCK.JED. The -n in the command line tells the program to produce a new log file, rather then append to the existing log file. The log file produced is CLOCK.LOG. The log file has a lot of interesting information about the programmed device the use of each device pin, the product term usage and the device pinout.

# A Memory Decoder

Let's take a look at a real life example that was suggested to me by Dave Baldwin. Let's say that we are designing a Z80 based system and we would like the memory map to include an 8K EPROM at address 0000h, a 2K EEPROM at address 2000h and have the remainder of the 64K address space filled with static ram (2 32K devices). So a table of our memory map looks like:

| Address (hex) | Device |

|---------------|--------|

| 0000-1FFF     | EPROM  |

| 2000-27FF     | EEPROM |

| 2800-7FFF     | SRAMO  |

| 8000-FFFF     | SRAM1  |

This type of decoding is a pain in the butt if we use standard TTL devices. We would need several devices and have to deal with the problems of propogation delays through the several levels of devices. If we use a 16V8 or 20V8 we can easily handle this decoding with one 20 or 24 pin device. Our total propogation delay will be the single propogation delay of the chip. This means we can have a propogation delay as low as 5 ns with a GAL rated at 5 ns. In addition we can include the decoding of the I/O space on the same chip.

```

Figure 4.

Q4 * /Q1 +

Q4 * /Q2 +

Q4 * /Q3

GCLK.EQN Logic Analyzer U15

This is the declaration section

CHIP GCLK 16V8

; SCO and SC1 output the system clock as selected

Pin labels here

CLK NC EXT SELF S2 S1 S0 DIR WR GND

by

; SO, S1 and S2

OEN SC1 WRDAT SCO Q4 Q3 Q2 Q1 Q0 VCC

Next is the equation section

SCO = /SO * /S1 * /S2 * SELF +

S0 * /S1 * /S2 * EXT +

S0 * S1 * /S2 * Q4 +

ÉQUATIONS

/S0 * /S1 * S2 * Q3 +

; QO - Q4 form a 5 bit binary counter

SO * /S1 * S2 * Q2 +

/S0 * S1 * S2 * Q1 +

QO :=

/00

SO * S1 * S2 * Q0

Q1 := Q0 * /Q1 +

SC1 = /S0 * /S1 * /S2 * SELF +

/Q0 * Q1

S0 * /S1 * /S2 * EXT +

S0 * S1 * /S2 * Q4 +

Q2 := Q0 * Q1 * /Q2 +

Q2 * /Q0 +

/S0 * /S1 * S2 * Q3 +

S0 * /S1 * S2 * Q2 + /S0 * S1 * S2 * Q1 +

Q2 * /Q1

S0 * S1 * S2 * Q0

Q3 := Q0 * Q1 * Q2 * /Q3 +

Q3 * /Q0 +

Q3 * /Q1 +

; WRDAT is a simple OR function of WR and DIR

Q3 * /Q2

WRDAT = WR +

Q4 := Q0 * Q1 * Q2 * Q3 * /Q4 +

DIR

Q4 * /Q0 +

```

In this case defining the equations for each chip select output is very straight forward. We want the EPROM chip select to be active when address lines A15, A14 and A13 are low and the Z80 MREQ signal is low. Since the active state of the EPROM chip select is low we would express the equation as:

/EPROM = /A15 \* /A14 \* /A13 \* /MREQ

The EEPROM chip select is only slightly more involved. The address range 2000-27ff is selected when A15, A14, A12, A11 and MREQ are low, while A13 is high. This gives the equation:

/EEPROM = /A15 \* /A14 \* A13 \* /A12 \* /A11 \* /MREQ

The first static ram has the most complicated equation (but still well within the capabilities of the 16V8). The 2800-7FFF address space can be thought of as three regions 2800-2FFF, 3000-3FFF and 4000-7FFF. The product terms defining each of these regions is then ORed together to define the complete equation as follows:

```

/SRAMO = /A15 * /A14 * A13 * /A12 * A11 * /MREQ + /A15 * /A14 * A13 * A12 * /MREQ + /A15 * A14 * /MREQ

```

It is obvious that the equation for the second static RAM's chip select is:

/SRAM1 = A15 \* /MREQ

The complete equation file with the I/O decoding using a 16V8 is printed above. If we wanted finer granularity on the I/O decode we could use a 20V8, this would give us 4 addition inputs for address lines, that could be included in the equations. If we wanted to have a 10 chip select outputs we could use a GAL22V10. Note that the pin out selected is arbitrary, in this case we could swap any of the input pins or any of the output pins just by redefining the pin list. This is a great aid if you do your own PC board design.

I think this example shows you why I use programmable logic wherever I can. We have reduced our decode logic to one 20 pin device. In doing so we have reduced the number of interconnects, saved PC board space, saved money and saved both circuit and PC board design time. In addition we have increased our design flexibility and helped our parts inventory. If we later find that we must have a 16K EPROM instead of the 8K EPROM, we can change our decode circuit by just reprogramming the GAL16V8. We can also replace our bin of spare TTL chips with few 16V8s. Once you start using programmable logic you can see the advantages continue to pile up.

```

Z80 memory and I/O decoder example - TCJ